# UNIVERSIDADE FEDERAL DE JUIZ DE FORA INSTITUTO DE CIÊNCIAS EXATAS PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

Frederico José Dias Möller

Mutações Adaptativas via Aprendizado por Reforço para Programação Genética Cartesiana Aplicada ao Projeto e Otimização de Circuitos Lógicos Combinacionais

#### Frederico José Dias Möller

Mutações Adaptativas via Aprendizado por Reforço para Programação Genética Cartesiana Aplicada ao Projeto e Otimização de Circuitos Lógicos Combinacionais

Dissertação apresentada ao Programa de Pós-Graduação em Ciência da Computação da Universidade Federal de Juiz de Fora como requisito parcial à obtenção do título de Mestre em Ciência da Computação. Área de concentração: Ciência da Computação

Orientador: Prof. Dr. Heder Soares Bernardino

Coorientador: Prof. Dr. Stênio Sã Rosário Furtado Soares

Ficha catalográfica elaborada através do Modelo Latex do CDC da UFJF com os dados fornecidos pelo(a) autor(a)

Möller, Frederico José Dias.

Mutações Adaptativas via Aprendizado por Reforço para Programação Genética Cartesiana Aplicada ao Projeto e Otimização de Circuitos Lógicos Combinacionais / Frederico José Dias Möller. – 2022.

69 f. : il.

Orientador: Heder Soares Bernardino

Coorientador: Stênio Sã Rosário Furtado Soares

Dissertação (Mestrado) – Universidade Federal de Juiz de Fora, Instituto de Ciências Exatas. Programa de Pós-Graduação em Ciência da Computação, 2022.

1. Programação Genética Cartesiana. 2. Otimização. 3. Circuitos Lógicos. I. Bernardino, Heder Soares, orient. II. Soares, Stênio Sã Rosário Furtado, coorient. III. Título.

#### Frederico José Dias Möller

Mutações Adaptativas via Aprendizado por Reforço para Programação Genética Cartesiana Aplicada ao Projeto e Otimização de Circuitos Lógicos Combinacionais

> Dissertação apresentada ao Programa de Pósgraduação em Ciência da Computação da Universidade Federal de Juiz de Fora como requisito parcial obtenção do título de Mestre em Ciência da Computação. Área de concentração: Ciência da Computação.

Aprovada em 12 de abril de 2022.

#### **BANCA EXAMINADORA**

Prof. Dr. Heder Soares Bernardino - Orientador

Universidade Federal de Juiz de Fora

Prof. Dr. Stênio Sã Rosário Furtado Soares - Coorientador

Universidade Federal de Juiz de Fora

Prof. Dr. Helio José Corrêa Barbosa

Universidade Federal de Juiz de Fora

Prof. Dr. Francisco Augusto Lima Manfrini

Instituto Federal do Sudeste de Minas Gerais

#### Juiz de Fora, 21/03/2022.

Documento assinado eletronicamente por Heder Soares Bernardino, Professor(a), em 12/04/2022, às 18:14, conforme horário oficial de Brasília, com fundamento no § 3° do art. 4° do <u>Decreto n°</u> 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por Stenio Sa Rosario Furtado Soares, Professor(a), em 11/07/2022, às 13:59, conforme horário oficial de Brasília, com fundamento no § 3° do art. 4° do Decreto nº 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por Helio Jose Correa Barbosa, Professor(a), em 11/07/2022, às 14:05, conforme horário oficial de Brasília, com fundamento no § 3° do art. 4° do Decreto n° 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por Francisco Augusto Lima Manfrini, Usuário Externo, em 11/07/2022, às 15:51, conforme horário oficial de Brasília, com fundamento no § 3° do art. 4° do Decreto nº 10.543, de 13 de novembro de 2020.

A autenticidade deste documento pode ser conferida no Portal do SEI-Ufjf (www2.ufjf.br/SEI) através do ícone Conferência de Documentos, informando o código verificador 0716816 e o código CRC 8010814F.

#### **AGRADECIMENTOS**

Agradeço primeiramente a Deus. Agradeço aos meus pais, por sempre terem priorizado minha educação e estimulado meus estudos. Meu pai por ter me mostrado diversos experimentos sobre eletricidade e mecânica, quando era pequeno e até ter comprado um livro de BASIC para mim, muito antes de eu ter qualquer base para compreender tal conteúdo. Minha mãe, que me fez ter gosto pela matemática, de quem eu acho que eu herdei qualquer talento que eu tenho para as ciências exatas. Agradeço às minhas irmãs e ao meu cunhado, por todo o suporte e inspiração. Agradeço à Letícia, por ter me ajudado a superar o meu desligamento da AMAN e redescobrir minha identidade no meio científico. Agradeço à professora Eugênia e ao professor Jabour, pelos anos de trabalho no PET, onde tive oportunidade de ter melhor contato com o método científico, com a experimentação e ao desenvolvimento acadêmico. Agradeço aos professores Luiz Oscar e Francisco Manfrini, bem como ao meu amigo Felipe Amaral, pois foram eles que me motivaram a tentar o mestrado. Agradeço aos professores Helder, Stênio e Luciana por toda orientação, ajuda e paciência durante esses 3 anos de trabalho. Agradeço ao Lucas Miller pelo suporte com a versão do código da CGP com o qual eu trabalhei. Agradeço à CAPES pela bolsa de mestrado. Agradeço à banca avaliadora: professores Hélio, Manfrini, Helder e Stênio, pela presença, paciência e pelos comentários que contribuíram tanto com a revisão deste texto, como para sustentação de trabalhos futuros.

#### **RESUMO**

A otimização de circuitos lógicos combinacionais pode levar a dispositivos eletrônicos mais rápidos e baratos, mas é um problema NP-completo. Os algoritmos determinísticos para esta tarefa são limitados a pequenos problemas e a lógica de dois níveis. Para resolver esse tipo de problema, recorre-se ao uso de meta-heurísticas e a Programação Genética Cartesiana (CGP) é amplamente adotada na literatura, dentre as alternativas de computação evolutiva. Na CGP, a mutação é tradicionalmente o único operador para gerar novas soluções candidatas. Assim, o desempenho dessa abordagem depende da eficiência de tal operador. Diferentes operadores de mutação foram propostos para a CGP, mas a maioria deles se diferencia apenas na escolha dos nós que serão modificados. Porém, na modificação dos nós a mutação atua de forma não enviesada. Existem trabalhos na literatura que propõem matrizes estáticas de enviesamento nas mutações do tipo de porta lógica para a CGP e tais trabalhos obtiveram bons resultados. Entretanto, o enviesamento adotado nesses trabalhos não varia ao longo da busca, de modo que não acompanham as mudanças que podem ocorrer no processo de otimização a depender da região do espaço de busca que a solução candidata se encontra. Portanto, uma mutação adaptativa via Aprendizado por Reforço (RL) é proposta aqui para a CGP. A chamada CGP-RL foi avaliada num conjunto de problemas de otimização de portas lógicas e em outro para a minimização do número de transistores de circuitos digitais combinacionais. A CGP-RL proposta conseguiu melhores soluções em 3 dos 5 problemas de otimização de portas lógicas quando comparada com uma CGP com mutação enviesada da literatura e melhores médias em quase 60% dos problemas testados nesse trabalho para a minimização do número de transistores quando comparada com uma CGP tradicional. Em seguida à CGP-RL, outra técnica foi desenvolvida focando na escolha do elemento do nó a ser modificado pelo operador de mutação: entradas e operação lógica. A Node CGP-RL conseguiu melhores médias em cerca de 75% dos problemas abordados alcançando também as melhores soluções, quando comparada com a CGP, em 13 dos 23 problemas analisados, apresentando soluções finais com até 10% menos transistores que a CGP.

Palavras-chave: Programação Genética. Otimização. Circuitos Lógicos.

#### ABSTRACT

Optimizing combinational logic circuits can lead to faster and cheaper electronic devices, but it is an NP-complete problem. The deterministic algorithms for this task are limited to small problems and two-level logic. To solve this type of problem, meta-heuristics are used and Cartesian Genetic Programming (CGP) is widely adopted in the literature, among the alternatives to evolutionary computation. In CGP, the mutation is traditionally the only operator to generate new candidate solutions. Thus, the performance of this approach depends on the efficiency of such an operator. Different mutation operators have been proposed for the CGP, but most of them differ only in the choice of nodes to be modified. However, when modifying nodes, the mutation acts in an unbiased way. There are works in the literature that propose static bias matrices in the mutations of the logic gate type for the CGP and such works obtained good results. However, the bias adopted in these works does not vary along the search, so they do not follow the changes that may occur in the optimization process depending on the region of the search space where the candidate solution is. Therefore, an adaptive mutation via Reinforcement Learning (RL) is proposed here for PGC. The so-called CGP-RL was evaluated in a set of logic gate optimization problems and another for minimizing the number of transistors in combinational digital circuits. The proposed CGP-RL achieved better solutions in 3 out of 5 logic gate optimization problems when compared to a skewed mutation CGP in the literature and better averages in almost 60% of the problems tested in this work for the minimization of the number of transistors when compared with a traditional PGC. After CGP-RL, another technique was developed, focusing on choosing the node element to be modified by the mutation operator: inputs and logic operation. The Node CGP-RL achieved better averages in about 75% of the problems addressed, also reaching the best solutions, when compared to the CGP, in 13 of the 23 problems analyzed, presenting final solutions with up to 10% fewer transistors than CGP.

Keywords: Genetic Programming. Optimization. Logical Circuits.

# LISTA DE ILUSTRAÇÕES

| Figura 1 -  | Circuito Somador Completo, que realiza a soma dos bits de entrada $A$ e $B$              |

|-------------|------------------------------------------------------------------------------------------|

|             | e do bit de transporte $C_{in}$ expressando o resultado nas saídas $S$ e no bit de       |

|             | transporte de saída $C_{out}$ . O somador completo tem esse nome, pois pode-se           |

|             | aumentar a quantidade de bits a serem somados ligando a saída $C_{out}$ de um            |

|             | somador na entrada $C_{in}$ de outro                                                     |

| Figura 2 –  | Circuito Somador Completo representado como um digrafo                                   |

| Figura 3 -  | Circuito Flip Flop JK, um circuito lógico sequêncial. Sua saída não depende              |

|             | apenas das entradas, mas também do estado anterior de suas saídas.    .    22            |

| Figura 4 -  | Circuito Flip Flop JK representado como um digrafo. É possível observar                  |

|             | o ciclo formado pelas saídas dos nós $n_n$ . Essa característica dos Circuitos           |

|             | Sequenciais é que faz com que suas saídas dependam de seu estado anterior. 22            |

| Figura 5 -  | Diagrama de construção de uma porta lógica do tipo NAND de acordo com a                  |

|             | tecnologia TTL                                                                           |

| Figura 6 –  | Saída $S$ do Circuito Somador Completo projetada pela soma de produtos. $26$             |

| Figura 7 –  | Saída $S$ do Circuito Somador Completo projetada pelo produto das somas. $26$            |

| Figura 8 -  | Distribuição de recompensas das alavancas em um caça-níqueis em um pro                   |

|             | blema do tipo $k$ -armed $b$ andits de 10 alavancas. Cada posição representa uma         |

|             | alavanca e sua distribuição de recompensas                                               |

| Figura 9 –  | Comparação dos valores médios de recompensa, por acionamento de alavanca                 |

|             | das estratégias gulosa e a $\epsilon$ -greedy com $\epsilon = 0.1$                       |

| Figura 10 – | Comparação entre valor médio de recompensa média obtida por iteração entre               |

|             | a estratégia gulosa e a $\epsilon$ -greedy e suas variações com inicialização de valores |

|             | otimistas. $\epsilon = 0.1 \dots 33$                                                     |

| Figura 11 – | Representação de uma solução da CGP                                                      |

| Figura 12 – | Genótipo de uma solução da CGP                                                           |

| Figura 13 – | Diagrama que demonstra o processo evolutivo da CGP tradicional 34                        |

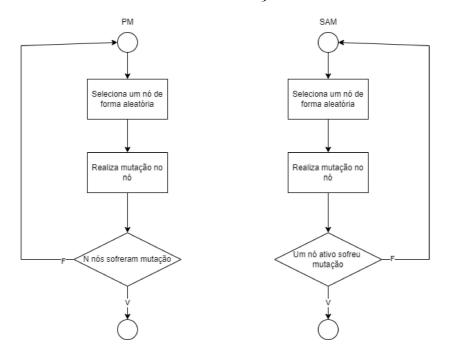

| Figura 14 – | Diagrama demonstrando o operador de mutação pontual (PM) em comparação                   |

|             | com o operador Single Active Mutation (SAM). Apenas a forma de decidir                   |

|             | quando parar de realizar as mutações muda                                                |

| Figura 15 – | Diagrama demonstrando o processo de mutação em um nó da CGP $37$                         |

| Figura 16 – | Matrizes de enviesamento de mutação propostas em (7)                                     |

| Figura 17 – | Relação da abordagem do problema de escolha de troca de portas lógicas                   |

|             | pelo operador de mutação da CPG com o problema alegórico dos k-armed                     |

|             | bandits                                                                                  |

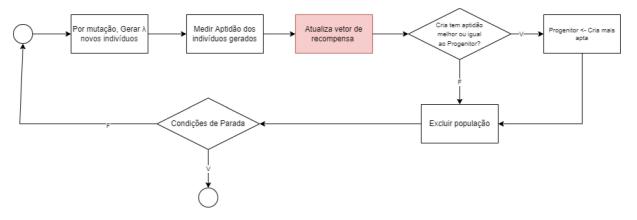

| Figura 18 – | Diagrama demonstrando o processo evolutivo da CGP-RL. A diferença com                    |

|             | relação à CGP tradicional são os passos em vermelho, correspondentes à                   |

|             | atualização da matriz de recompensas de troca de portas                                  |

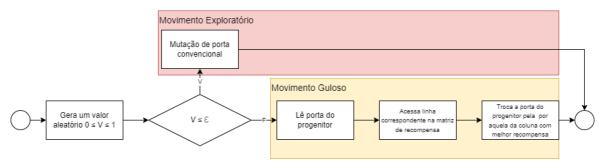

| Figura 19 – | Mutação do tipo de porta lógica pela CGP-RL. O movimento exploratório se refere à mutação não enviesada da CGP tradicional. No movimento guloso a CGP-RL vai sempre executar a troca na qual há a melhor recompensa média                                                                                                                                                                              |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figura 20 – | obtida                                                                                                                                                                                                                                                                                                                                                                                                 |

| Figura 21 – | relação À CGP-RL é a ausência do desvio condicional para mutações do tipo de porta: Qualquer individuo que foi gerado por uma mutação em um nó ativo contribui para a atualização do vetor de recompensas                                                                                                                                                                                              |

| Figura 22 – | mutação no movimento guloso                                                                                                                                                                                                                                                                                                                                                                            |

| Figura 23 – | o valor de I1G desconsiderando as mutações em nós cujo a porta lógica é do tipo NOT                                                                                                                                                                                                                                                                                                                    |

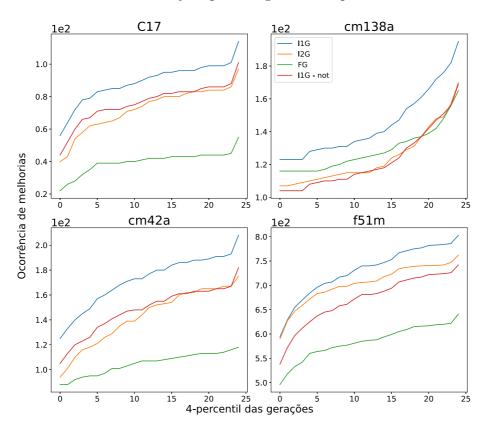

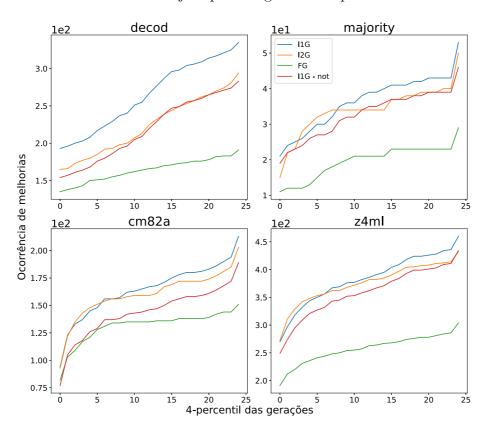

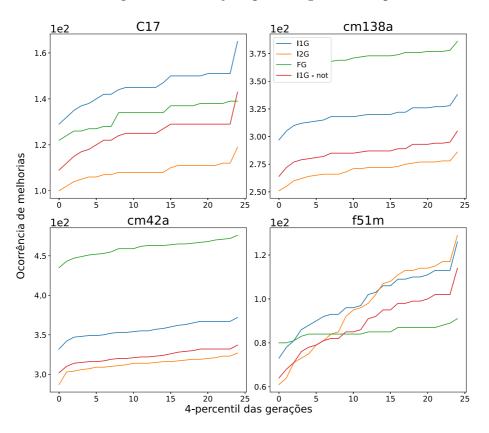

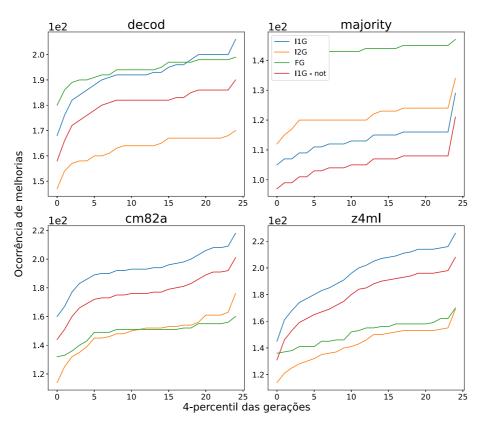

| Figura 24 – | o valor de I1G desconsiderando as mutações em nós cujo a porta lógica é do tipo NOT                                                                                                                                                                                                                                                                                                                    |

|             | durante a fase de otimização, onde o objetivo é reduzir o total do circuito factível.I1G representa melhorias geradas por mutação na primeira entrada, I2G na segunda entrada e FG mutações no tipo de porta lógica. I1G - not representa o valor de I1G desconsiderando as mutações em nós cujo a porta lógica é do tipo NOT                                                                          |

| Figura 25 – | Ocorrência de melhorias nos quatro últimos problemas de tamanho pequeno, durante a fase de otimização, onde o objetivo é reduzir o total do circuito factível.IIG representa melhorias geradas por mutação na primeira entrada, I2G na segunda entrada e FG mutações no tipo de porta lógica. I1G - not representa o valor de I1G desconsiderando as mutações em nós cujo a porta lógica é do tipo NOT |

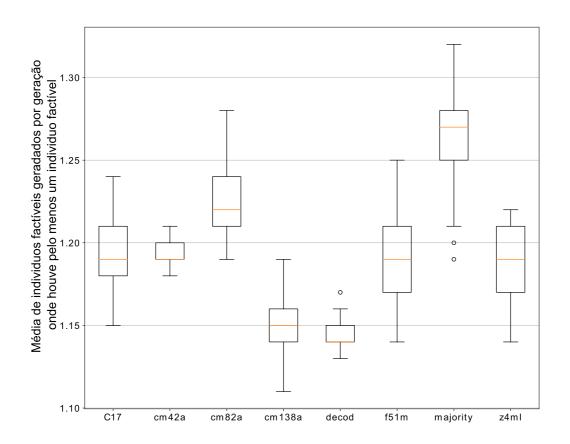

| Figura 2 | 26 – | Ocorrência média de indivíduos factíveis, em gerações onde ao menos um dos  |

|----------|------|-----------------------------------------------------------------------------|

|          |      | indivíduos gerados é factível                                               |

| Figura : | 27 – | Gerações onde pelo menos um indivíduo factível foi gerado                   |

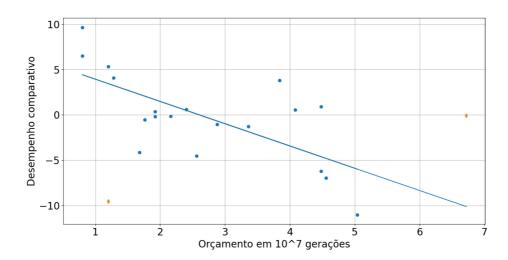

| Figura 2 | 28 – | Índices de desempenho $P_{RRL,R}$ e orçamentos computacionais dos problemas |

|          |      | aqui resolvidos. Os problemas decode e frg1 são marcados como losangos      |

|          |      | laranja                                                                     |

# LISTA DE TABELAS

| Tabela 1 –  | Tabela verdade do circuito Somador Completo                                              | 23         |

|-------------|------------------------------------------------------------------------------------------|------------|

| Tabela 2 –  | Número de transistores por porta lógica de acordo com a tecnologia TTL.                  | 25         |

| Tabela 3 –  | Problemas usados para comparar os algoritmos                                             | 46         |

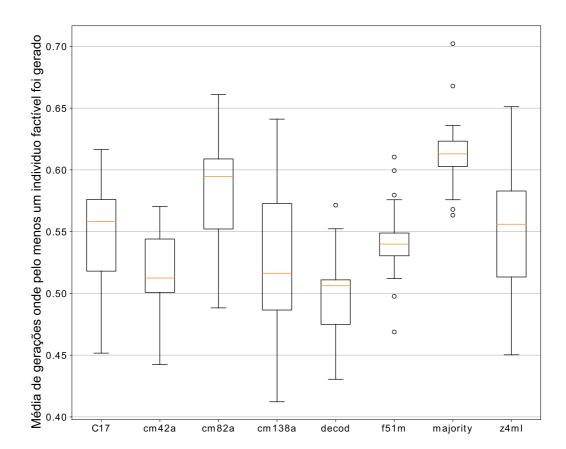

| Tabela 4 -  | Média de gerações nas quais houve pelo menos um individuo factível gera                  | do         |

|             | durante a fase de otimização, na CGP e na $Node$ CGP-RL                                  | 51         |

| Tabela 5 -  | Resultados comparativos entre a CGP-RL e CGP usando apenas SAM.                          | 53         |

| Tabela 6 –  | Comparação dos resultados da CGP-RL com o melhor método proposto e                       | m          |

|             | (7). Melhor significa a menor quantidade de portas que o algoritmo consegu               | ıiu        |

|             | para o relativo problema. TS é a taxa de sucesso do algoritmo, Média é                   | a          |

|             | média de portas que o algoritmo conseguiu e DP é o desvio padrão                         | 56         |

| Tabela 7 –  | Análise de performace para $\alpha \in \{0.1, 0.2, \dots, 1.0\}$                         | 58         |

| Tabela 8 –  | Análise de performance para $\alpha \in \{0.1, 0.2, \dots, 1.0\}$ por tamanho de problem | na.        |

|             | M significa Melhor and $Ns$ significa Nscore                                             | 58         |

| Tabela 9 –  | Comparação entre CGP com apenas SAM, CGP-RL (33), Node CGP-F                             | ₹L         |

|             | não estacionária (ns) com $\alpha=0.6$ e Node CGP-RL estacionária (s)                    | 59         |

| Tabela 10 – | Resultados obtidos pela Node CGP-RL e pela CGP usando apenas o operad                    | lor        |

|             | SAM, inicializadas com população aleatória (R) e factível (E). Nos algoritm              | os         |

|             | das colunas R, os problemas alu2 e cmb aparecem sem dados onde est                       | es         |

|             | falharam em geral alguma solução factível ao final da fase de projeto.                   | Ο          |

|             | problema alu4 não foi executado para o algoritmo Node CGP-RL devido                      | à          |

|             | restrições na disponibilidade de recursos computacionais                                 | 60         |

| Tabela 11 – | Resultados obtidos pela <i>Node</i> CGP-RL com o ajuste para evitar o env                | ie-        |

|             | samento da porta NOT, a Node CGP-RL sem o ajuste e a CGP usando                          | a          |

|             | mutação SAM. Problemas onde os dados estão preenchidos com - "significa                  | $^{ m lm}$ |

|             | que o algoritmo não conseguiu gerar uma solução factível me nenhuma d                    | as.        |

|             | execuções independentes                                                                  | 63         |

#### LISTA DE ABREVIATURAS E SIGLAS

- $(\operatorname{CGP})$  Cartesian Genetic Programming Programação Genética Cartesiana

- (CLC) Combinationla Logic Circuits Circuitos Lógicos combinacionais

- (PM) Point Mutation Operador de mutação pontual

- (RL) Reiforced Learning Aprendizado por reforço

- $({\rm SAM})$  Single Active Mutation Operador de única mutação ativa

- (TTL) Transistor-Transistor Logic Lógica Tansistor-Transistor

# SUMÁRIO

| 1     | INTRODUÇÃO                                                            |  |

|-------|-----------------------------------------------------------------------|--|

| 1.1   | OBJETIVOS                                                             |  |

| 2     | REVISÃO BIBLIOGRÁFICA                                                 |  |

| 2.1   | HISTÓRICO                                                             |  |

| 2.2   | ABORDAGENS EVOLUTIVAS                                                 |  |

| 2.3   | PROGRAMAÇÃO GENÉTICA CARTESIANA                                       |  |

| 2.4   | USO DO APRENDIZADO POR REFORÇO NA COMPUTAÇÃO EVOLU-                   |  |

|       | TIVA                                                                  |  |

| 3     | FUNDAMENTOS DE CIRCUITOS DIGITAIS 20                                  |  |

| 3.1   | CIRCUITOS LÓGICOS                                                     |  |

| 3.2   | TABELA VERDADE                                                        |  |

| 3.3   | PORTAS LÓGICAS                                                        |  |

| 3.4   | PROJETO DE CIRCUITOS LÓGICOS COMBINACIONAIS 25                        |  |

| 4     | APRENDIZADO POR REFORÇO                                               |  |

| 4.1   | O PROBLEMA DO $K$ -ARMED BANDITS E A ESTRATÉGIA $\epsilon$ -GREEDY 27 |  |

| 4.1.1 | Inicialização com valores otimistas                                   |  |

| 4.1.2 | Estratégia para problemas não estacionários                           |  |

| 5     | PROGRAMAÇÃO GENÉTICA CARTESIANA 33                                    |  |

| 5.1   | OPERADORES DE MUTAÇÃO                                                 |  |

| 6     | MÉTODO PROPOSTO                                                       |  |

| 6.1   | CGP-RL                                                                |  |

| 6.2   | <i>Node</i> CGP-RL                                                    |  |

| 7     | EXPERIMENTOS COMPUTACIONAIS 45                                        |  |

| 7.1   | ANÁLISES SOBRE A CGP                                                  |  |

| 7.2   | AVALIAÇÃO COMPARATIVA DA CGP-RL                                       |  |

| 7.2.1 | Comparação da CGP-RL com a CGP usando viés estático 54                |  |

| 7.3   | ANÁLISES SOBRE NODE CGP-RL                                            |  |

| 7.3.1 | Estudo da variação do valor $\alpha$                                  |  |

| 7.3.2 | Análise comparativa dos resultados da <i>Node</i> CGP-RL com a CGP    |  |

|       | CGP-RL                                                                |  |

| 7.3.3 | Análise do enviesamento da primeira Entrada 61                        |  |

| 8     | CONCLUSÃO                                                             |  |

|       | REFERÊNCIAS                                                           |  |

## 1 INTRODUÇÃO

Circuitos lógicos Combinacionais (CLCs) são sistemas onde as saídas são resultados de funções lógica temporalmente independentes de suas entradas (36, 34). Tais circuitos são elementos fundamentais na eletrônica digital, campo de estudos que trata do projeto e manutenção de dispositivos que utilizam sinais discretos para seu funcionamento (36). A eletrônica digital é um campo tecnológico bastante demandado pela humanidade. Portanto, o bom projeto de CLCs implica em economia material e, portanto, barateamento de preços e aumento da acessibilidade a equipamentos eletrônicos digitais, como computadores, celulares, relógios entre outros. Tal otimização também pode implicar em redução de tamanho, de calor dissipado e tempo de resposta. Todavia, a minimização destes é um problema de otimização lógica, que é um problema NP completo e os métodos determinísticos existentes não são práticos para a maioria das aplicações (38).

A abordagem comum é usar heurísticas como o algoritmo ESPRESSO (1) que é bastante adotado para a minimização de CLCs. Este método opera manipulando "cubos" que representam o produto dos mintermos da expressão lógica do circuito a ser minimizado. O EXPRESSO consegue chegar em soluções de boa qualidade com baixo custo de tempo e memória na maioria dos problemas.

Uma alternativa ao ESPRESSO são os métodos evolutivos, que em geral conduzem à melhores soluções (8). Dentre estes, destaca-se a Programação Genética Cartesiana (CGP) (27). Na CGP, os circuitos são representados como dígrafos acíclicos e cada nó possui uma função lógica associada. A CGP geralmente gera novos indivíduos por meio de mutação que, neste caso, consiste na alteração de uma das entradas de um nó, ou de sua função lógica. A CGP é capaz não apenas de projetar um circuito lógico combinacional que atenda a uma tabela verdade alvo, mas também de minimizar alguns atributos desejados, como o número de transistores.

Há diversos trabalhos na literatura propondo alterações na CGP para melhorar seu desempenho. Propostas como o *crossover* sobre o fenótipo descrito em (6) aumentam significantemente o custo em tempo da CGP. Outras, como o método semanticamente orientado visto em (15) dependem da avaliação usando a tabela verdade, o que torna o custo computacional do método muito alto para circuitos com muitas entradas.

Outra abordagem que tem sido bastante usada na literatura, não só relativa à CGP, mas em Computação Evolutiva em geral é o enviesamento de operadores. Trabalhos como (24) usaram a estratégia  $\epsilon$ -greedy para selecionar os melhores operadores evolutivos para gerar novos indivíduos ao longo da execução de um algoritmo genético. Em (7), os autores propuseram uma matriz de enviesamento para a mutação de portas lógicas na CGP com valores estáticos.

Uma extrapolação da técnica apresentada em (7) é a construção da matriz de

enviesamento usando o aprendizado de máquina. A estratégia  $\epsilon$ -greedy, uma técnica de balanço de estratégias exploratórias e gulosas, foi aplicada nas mutações do tipo de porta lógica, gerando a primeira técnica proposta aqui: a CGP-RL (33). Outra técnica proposta foi a Node CGP-RL (32), que aplica o mesmo princípio, mas em outro momento da mutação de um nó: a escolha de qual elemento vai sofrer mutação: entradas ou função lógica. Ambas as técnicas, usando uma estratégia de baixa complexidade, apresentaram melhoras no resultado da CGP aplicada ao projeto e otimização de CLCs.

#### 1.1 OBJETIVOS

O objetivo principal dos trabalhos realizados é melhorar o desempenho da CGP quando aplicada ao projeto e otimização da quantidade de transistores de CLCs, propondo dois operadores adaptativos, CGP-RL e *Node* CGP-RL,baseado em aprendizado. Os trabalhos têm também como objetivos secundários:

- Analisar o processo de mutação da CGP, buscando entender como cada elemento impacta na geração de melhores soluções ao longo do processo evolutivo;

- Propor um operador de aprendizado por reforço para enviesar a mutação de portas lógicas da CGP; e

- Propor um operador de aprendizado por reforço para enviesar a mutação de nós da CGP;

#### 2 REVISÃO BIBLIOGRÁFICA

#### 2.1 HISTÓRICO

Apesar da existência de dispositivos que utilizavam sinais eletrônicos discretizados para realizar tarefas, como computadores de relés e valvulados. O marco que consolidou a eletrônica digital foi a invenção do transistor em 1947, por William Shockley, John Bardeen e Walter Brattian no Bell Laboratories. Tal invenção lhes rendeu o prêmio Nobel de Física em 1956. De tal outras tecnologias surgiram, como o Circuito Integrado, que rendeu à Jack Kilby em 1958 e o primeiro microprocessador integrado, o intel 4004, em 1971 (39).

A complexidade dos circuitos lógicos tem crescido com o tempo, ainda que de forma linear (13). A demanda e produção de circuitos digitais também tem crescido, de forma geral exponencialmente (22). Portanto a é justificada a necessidade de métodos automáticos de projeto e otimização de circuitos lógicos.

Tradicionalmente, se adotam técnicas top down, que consistem em decompor os circuitos em sub-circuitos, de menor complexidade e portanto mais fáceis de projetar e otimizar (29). Abordagens bottom up consistem em resolver problemas pontuais no sistema e então ir integrando essas soluções em circuitos de maior complexidade. Tal abordagem tende a gerar circuitos com menor redundância e mais simplificados (29), porém exige técnicas de maior complexidade, como as abordagens evolutivas. As abordagens evolutivas não são as únicas técnicas de inteligência computacional propostas para projetar circuitos em uma abordagem bottom up, porém são as que apresentam melhores resultados (19).

#### 2.2 ABORDAGENS EVOLUTIVAS

Abordagens evolutivas para o projeto de circuitos lógicos podem ser traçadas desde 1956, com o trabalho de Friedman (11). Que utilizou analogias com o desenvolvimento do sistema nervoso para projetar hardware,

Todavia, foi o algoritmo genético de Loius, em 1993 que expandiu os trabalhos feitos nessa área. A codificação do genoma adotada em seu trabalho foi uma matriz onde cada elemento representa uma porta lógica e suas entradas (23). Tal algoritmo pesquisa primeiramente por soluções que atendam todas as linhas da tabela verdade do circuito desejado e depois as classifica pelo número de portas WIRE, ou seja, portas que significam uma ligação direta entre duas outras portas. Ele então entrega o circuito com maior número de portas WIRE que cumpre a tabela verdade desejada.

Tal codificação de genoma também foi usada em (27). A diferença da abordagem de Miller et al para a de Loius é que Miller aumentou o espaço de busca adicionando a possibilidade de cada elemento da matriz, além de ser uma porta lógica, ser também um

multiplexador 2x1.

Outra proposta, criada a partir da codificação de Louis foi o algoritmo NGA (*N-cardinality Genetic Algorithm*), que consiste em inicializar o algoritmo de Louis com uma matriz pequena e ir aumentando o tamanho da mesma até que uma solução seja encontrada (5). Os mesmos autores de (5), também propuseram uma variação multiobjetivo, que não só projetava o circuito, mas também buscava maximizar o número de portas WIRE (4).

## 2.3 PROGRAMAÇÃO GENÉTICA CARTESIANA

A Programação genética cartesiana (CGP) é uma abordagem evolutiva cujo a codificação do genoma é feita na forma de dígrafos acíclicos (27, 28, 30). Os nós de tal dígrafo são organizados de forma matricial em linhas e colunas e cada nó possui informação de suas entradas e tipo de porta lógica, em codificação similar à de Louis. A CGP será explicada de forma mais detalhada no Capítulo 5.

A maior parte do genótipo na CGP não é mapeada no fenótipo (37). No entanto, o genótipo não mapeado carrega informações evolutivas de forma análoga ao que acontece com o DNA não codificante na biologia. Tal informação, ao longo do processo evolutivo, pode voltar a compor a parte do genótipo mapeada para o fenótipo, contribuindo para gerar novas soluções e sendo uma das características que ajudam a CGP a evitar ótimos locais (37).

A CGP tem melhor desempenho no projeto e otimização de circuitos lógicos que os demais métodos de Programação Genética (12). A CGP não apresenta o problema de aumento desordenado da solução, uma vez que o tamanho de cada individuo é limitado durante todo o processo evolutivo. Além disso, o indivíduo na CGP apresenta um formato otimizado para a representação de circuitos combinacionais lógicos, com cada individuo representando um circuito por completo, com todas as suas saídas (28).

Diversas alterações foram propostas para a CGP desde sua criação. O operador de mutação do tipo SAM (Single Active Mutation) que será detalhado no Capítulo 5, modifica a forma como a CGP escolhe quais nós serão modificados. Um único nó ativo é modificado por geração (12). O operador SAM tem apresentado melhor desempenho na otimização e projeto de CLC que o operador tradicional da CGP e outros operadores propostos, como o GAM (Guided Active Mutation) (12, 8), que é uma versão baseada no SAM que atua em subgrafos que o pior resultado com relação à tabela verdade desejada.

A CGP não usa tradicionalmente um operador de *crossover* (28). Tal operador chegou a ser utilizado inicialmente na CGP, mas mas se mostrou disruptivo e portanto abandonado (28, 6). Operadores *crossover* foram propostos e investigados em (3, 18, 40, 2). (6) propôs um operador que faz a recombinação com base no fenótipo do individuo, apresentando resultados promissores.

Um dos maiores desafios da CGP é a escalabilidade (28, 15). Na literatura, os circuitos multiplicador 5x5 e somador 9+9 são os de maior complexidade que a CGP conseguiu gerar um individuo factível à partir de uma população aleatória (16). Propostas como o Operador Semanticamente Orientado (15) e o operador de mutação enviesado proposto em (7) tem dentre seus objetivos superar tal problema.

O Operador Semanticamente Orientado (SOMO) mapeia a saída esperada de um nó para um conjunto de entradas e então modifica uma de suas entradas para algum nó em colunas anteriores que torne a saída do nó que sofrendo mutação se aproxime da saída desejada. O SOMO consegue gerar um Somador 9+9 em cerca de pouco menos de três horas, um somador 10+10 em cerca de vinte de duas horas e um multiplicador 5x5 em cerca de quarenta e duas horas (15). Tais resultados não são apenas melhorias no desempenho da CGP como também um indicativo de que o problema de escalabilidade pode vir a ser resolvido com modificações que direcionem as decisões do operador de mutação (15).

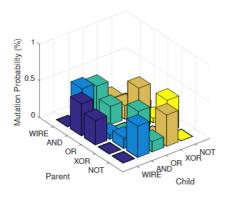

O operador enviesado proposto em (7) possui uma matriz que guia a mutação de portas lógicas em um nó. As linhas de tal matriz representam a porta lógica do nó que vai sofrer mutação e as colunas representam para qual tipo de porta esta vai ser modificada. Os valores de cada célula são um peso que influencia na probabilidade de tal troca acontecer. Dessa forma, trocas que são consideradas vantajosas tem maior chance de ocorrer.

#### 2.4 USO DO APRENDIZADO POR REFORCO NA COMPUTAÇÃO EVOLUTIVA

De maneira geral, abordagens evolutivas envolvem uma população inicial de soluções, a criação de novas soluções a partir desta população e a seleção das melhores soluções para compor a próxima geração. Há uma grande variação na forma como executar cada uma das etapas. Existem métodos que usam a recombinação junto com a mutação para gerar novas soluções, outros que usam apenas a mutação (9). Para determinadas abordagens a melhor forma de selecionar as melhores soluções é o ranqueamento, que é o ordenamento das soluções de acordo com sua aptidão para então selecionar as melhores, para outras é a estratégia de roleta, onde cada solução tem uma probabilidade de ser selecionada para a próxima geração de acordo com suas aptidão. Existem outros métodos de seleção de soluções. Cada uma dessas formas possuem variações ou parâmetros que precisam ser ajustados de acordo com a abordagem evolutiva, contexto, ou problema (9).

Abordagens usando aprendizado de máquina vem otimizando esses ajustes. Em (25), os autores desenvolveram uma técnica que usa Aprendizado por Reforço (RL) para ajuste de parâmetros em um Algoritmo Genético na resolução de problemas de Satisfatibilidade Booleana, ou seja, determinar se existe um conjunto de valores para variáveis de uma expressão lógica que torne a expressão verdadeira, um problema complexo da classe NP-

completo e computacionalmente custoso. Em (24), os autores usaram o RL para escolher quais operadores seriam usados para gerar um novo indivíduo. O trabalho (17) propõe uma abordagem dinâmica do problema dos k-armed bandits também para a seleção de operadores, apresentando bons resultados.

A CGP, como método de computação evolutiva, está sujeita aos problemas de escolha de operadores e ajustes de parâmetros. Na mutação do tipo de nó, o operador tem que decidir qual elemento do nó vai sofrer alteração e como essa mutação vai acontecer. De forma tradicional essa decisão é feita de forma não enviesada, mas em (7) foi apontado que um enviesamento na mutação de portas lógicas pode levar a melhores resultados que uma abordagem neutra. Por outro lado em (15), um direcionamento para a mutação de entradas ajuda na convergência da CGP para uma solução factível. Os problemas de decisão de qual elemento do nó vai sofrer mutação, bem como qual mutação de porta lógica vai acontecer se encaixam no modelo do problema dos k-armed bandits e portanto uma estratégia RL, inspirada nos trabalhos (24, 17) pode melhorar o desempenho do operador de mutação de nós e de portas lógicas.

#### 3 FUNDAMENTOS DE CIRCUITOS DIGITAIS

As técnicas de Programação Genética Cartesiana abordadas nesse trabalho são aplicadas ao projeto e otimização de circuitos lógicos combinacionais. Tais circuitos trabalham com sinais digitais, ou seja, sinais representados por valores que variam de forma discreta (36). Neste capítulo serão abordados conceitos fundamentais de eletrônica e lógica digital.

### 3.1 CIRCUITOS LÓGICOS

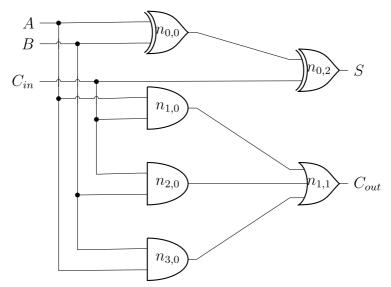

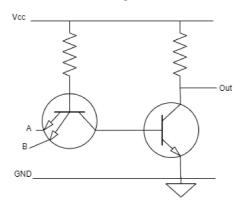

Circuitos lógicos são sistemas que processam informações usando funções Booleanas (36, 34). Tais são constituídos de variáveis de entrada e de saída, e portas lógicas. A Figura 1 representa um circuito Somador Completo. Tal circuito realiza a soma de dois bits (entradas A e B) e do bit de transporte de outro Somador Completo  $C_{in}$ . O resultado é expresso na saída S e se o valor da soma for maior que 1, no bit de transporte de saída  $C_{out}$ .

Figura 1 – Circuito Somador Completo, que realiza a soma dos bits de entrada A e B e do bit de transporte  $C_{in}$  expressando o resultado nas saídas S e no bit de transporte de saída  $C_{out}$ . O somador completo tem esse nome, pois pode-se aumentar a quantidade de bits a serem somados ligando a saída  $C_{out}$  de um somador na entrada  $C_{in}$  de outro.

Fonte: Figura produzida pelo autor.

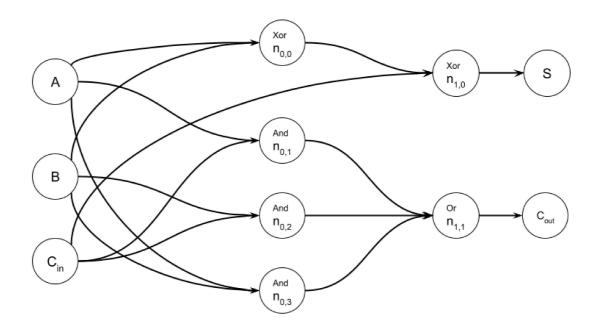

Figura 2 – Circuito Somador Completo representado como um digrafo.

Fonte: Figura produzida pelo autor

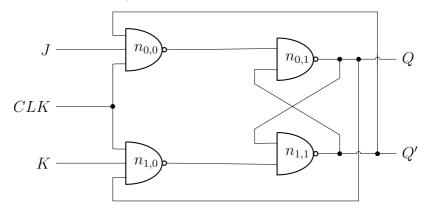

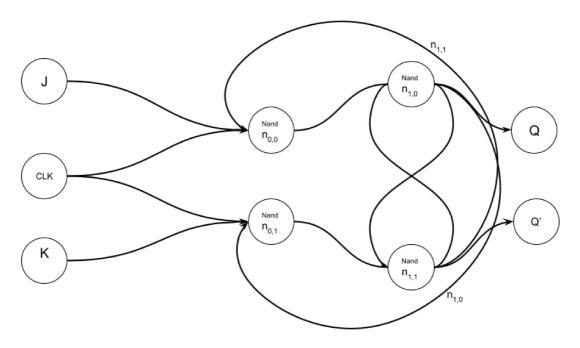

No caso do circuito Somador Completo, é possível observar que cada saída depende exclusivamente dos valores das entradas. O valor das saídas anteriores não interfere no valor da saída atual, ou seja as saídas são independentes do tempo. Para esse tipo de circuito lógico é dado o nome de circuitos lógicos combinacionais (CLC). Outro tipo de circuitos lógicos são os sequenciais A Figura 3 representa um Flip Flop JK. A Figura 2 e a Figura 4 são a representação em grafos dos circuitos Somador Completo e Flip Flop JK. Observando a representação em grafos é possível notar que a diferença fundamental é a ausência de ciclos no CLC. Por conveniência, será adotada a representação dos circuitos pela forma de grafos a partir deste ponto do trabalho.

Figura 3 – Circuito Flip Flop JK, um circuito lógico sequêncial. Sua saída não depende apenas das entradas, mas também do estado anterior de suas saídas.

Fonte: Figura produzida pelo autor

Figura 4 – Circuito Flip Flop JK representado como um digrafo. É possível observar o ciclo formado pelas saídas dos nós  $n_n$ . Essa característica dos Circuitos Sequenciais é que faz com que suas saídas dependam de seu estado anterior.

Fonte: Figura produzida pelo autor.

#### 3.2 TABELA VERDADE

Como quantidade de variáveis de entrada e de saída de um circuito lógico são finitas e os valores que cada uma pode assumir é apenas Verdadeiro ou Falso, é possível mapear cada entrada possível com sua saída e assim gerar o artefato conhecido como tabela verdade. A Tabela 1 é a tabela verdade de um Somador Completo. Dois circuitos lógicos são logicamente idênticos, isto é, desempenham a mesma função lógica, se suas

tabelas verdades forem idênticas. A tabela possui  $n_i + n_o$  colunas, onde  $n_i$  é o número de variáveis de entrada do circuito e  $n_0$  é o número de variáveis de saída. Portanto, as  $n_i$  primeiras colunas da tabela representam cada uma das variáveis de entrada e seus estados, enquanto as últimas colunas representam os estados das variáveis de saída. Desta forma, cada linha da tabela verdade representa um possível valor de entrada do circuito e seu valor de saída associado. Várias saídas podem ter o mesmo valor, mas cada valor de entrada é único.

Tabela 1 – Tabela verdade do circuito Somador Completo.

| $\overline{A}$ | В | $C_{in}$ | $C_{out}$ | S |

|----------------|---|----------|-----------|---|

| 0              | 0 | 0        | 0         | 0 |

| 0              | 0 | 1        | 0         | 1 |

| 0              | 1 | 0        | 0         | 1 |

| 0              | 1 | 1        | 1         | 0 |

| 1              | 0 | 0        | 0         | 1 |

| 1              | 0 | 1        | 1         | 0 |

| 1              | 1 | 0        | 1         | 0 |

| 1              | 1 | 1        | 1         | 1 |

Fonte: Elaborada pelo autor.

O método tradicional de comparação de Circuitos Lógicos envolve medir a distância de Hamming de acordo as saídas das tabelas verdade dos circuitos. A distância de Hamming é uma métrica de comparação entre duas cadeias de valores de mesmo tamanho e contabiliza quantas posições tem valores diferentes. Na comparação de circuitos, pode-se obter tal distância comparando as saídas das tabelas verdade de acordo com a Equação 3.1, onde i é a linha da tabela verdade, o a saída, o e o a quantidade de variáveis de entrada, o a quantidade de variáveis de saída e o e o o e o0 são os valores das saídas o0 dos circuitos o0 e o0, na linha o0 o0 tamanho da tabela verdade é exponencialmente proporcional à quantidade de variáveis de entrada de um circuito e isso torna esse cálculo computacionalmente custoso para circuitos com maiores quantidades de variáveis de entrada.

$$h(a,b) = \sum_{i=1}^{i=2^{n_i}} \sum_{o=1}^{o=n_o} |a_{i,o} - b_{i,o}|$$

(3.1)

Uma alternativa para verificar a similaridade lógica de circuitos é fazer sua comparação por diagramas de decisão binários (BDD). BDDs são digrafos acíclicos que representam de forma comprimida a relação das variáveis de entrada de um circuito lógico com seu valor de uma de suas saídas. O uso de BDDs para a comparação de circuitos lógicos é reconhecido na literatura como um método menos custoso que a comparação de tabelas verdade (8) e é o método de comparação de circuitos adotado neste trabalho.

#### 3.3 PORTAS LÓGICAS

Portas lógicas são os blocos fundamentais de construção de um circuito lógico e representam as funções lógicas básicas (36). Comumente, as portas lógicas estão relacionadas às funções lógicas mais simples, como AND, OR, ou NOT. Porém, existem portas mais complexas, como as chamadas superportas. Não existe uma porta lógica fundamental, ou seja, que não pode ser construída a partir de outras. Qualquer tabela verdade de uma porta lógica pode ser construída a partir de portas NOR e NAND e essas podem ser construídas a partir de outras portas lógicas (34).

Portas lógicas ideais realizam a operação lógica de forma instantânea e sua saída é sempre um valor booleano. Isso não acontece nas portas lógicas aplicadas na eletrônica digital. Elas possuem um tempo de atraso de resposta e suas saídas são um valor de tensão não inteiro. De acordo com a tecnologia de construção, elas são sujeitas à ruído, perda de potência e interferências do meio.

A tecnologia de construção de portas lógicas utilizada como referência neste trabalho é a Transistor-Transistor Logic, ou Logica Transistor-Transistor (TTL). Tal tecnologia utiliza transistores de junção bipolar tanto para executar a operação lógica, quanto para amplificar o sinal dentro do circuito da porta. (10). Portas lógicas TTL operam com tensão entre 0V e 5V, sendo o sinal baixo (falso) entre 0V e 0,5V e o alto (verdadeiro) entre 2,7V e 5V, porém com as tolerâncias ao ruído sendo consideradas o sinal baixo passa a ser entre 0V e 0,8V e o alto entre 2V e 5V. A Tabela 2 relaciona a quantidade de transistores por porta lógica TTL e a Figura 5 apresenta o diagrama de uma porta NAND construída em tal tecnologia. Todas as portas possuem duas entradas exceto a NOT.

Figura 5 – Diagrama de construção de uma porta lógica do tipo NAND de acordo com a tecnologia TTL.

Fonte: Figura produzida pelo autor.

Tabela 2 – Número de transistores por porta lógica de acordo com a tecnologia TTL.

| Porta Lógica | Número de transistores |

|--------------|------------------------|

| NOT          | 1                      |

| AND          | 2                      |

| OR           | 2                      |

| NAND         | 2                      |

| NOR          | 1                      |

| XOR          | 3                      |

| XNOR         | 4                      |

Fonte: EREN, 2003.

Uma vez que o aspecto físico de um CLC é dado pelos elementos de construção de suas portas lógicas, é natural que estratégias de otimização foquem nesses elementos ao invés de focar nas portas lógicas. Tal abordagem foi evidenciada em (8), que vinculou o valor da quantidade de transistores para cada porta lógica e fez a minimização dos CLCs comparando a quantidade de transistores. A mesma abordagem é utilizada aqui. Apesar de existirem tecnologias mais modernas, como a CMOS, o trabalho de referência (8) utiliza a tecnologia TTL, portanto tal abordagem foi mantida neste estudo.

#### 3.4 PROJETO DE CIRCUITOS LÓGICOS COMBINACIONAIS

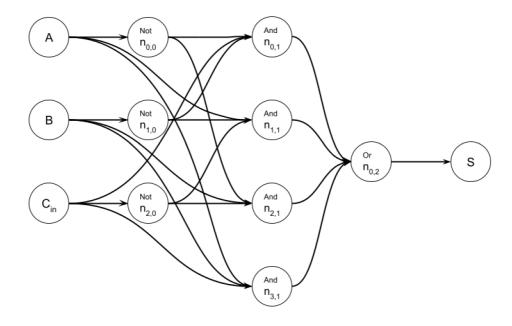

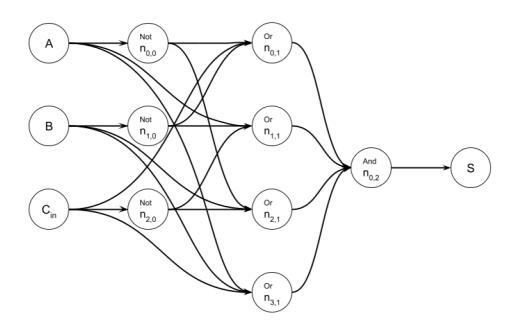

É possível projetar um CLC a partir de sua tabela verdade. Um método simples de se fazer isso é usar a soma dos produtos: para cada linha da tabela verdade onde uma determinada saída o tem valor "1", lê-se os valores das variáveis de entrada dessa linha e cria-se um elemento contendo o produto das variáveis que estão com valor "1" com a negação das variáveis com valor "0". No fim, cada elemento é somado e essa soma de produtos corresponde à expressão lógica daquela saída. A soma dos produtos pode ser traduzida em um circuito lógico fazendo-se com que cada elemento negado se transforme em uma porta NOT, os conjuntos de produtos em uma sequência de portas AND e a soma em uma sequência de portas OR. É possível fazer processo similar e projetar o circuito usando produtos da soma. A Figura 6 mostra a saída S do Somador Completo como uma soma de produtos enquanto a Figura 7 mostra a saída S como um produto de somas.

Esses métodos, no entanto, não são ideais, pois acaba gerando circuitos muito grandes, o que aumenta seu custo e pode gerar diversas características negativas, como atraso no tempo de resposta, consumo energético e potência dissipada em forma de calor. Existem métodos determinísticos como o mapa de Karnaugh (20) e o método de Quine - McCluskey (26) conseguem entregar circuitos otimizados dentro do escopo de lógica de dois níveis, utilizando apenas as portas NOT, AND e OR. Porém tais métodos não são práticos para problemas maiores, devido a sua complexidade e nem se aplicam à lógica

multi-nível que utiliza um conjunto maior de tipos de portas lógicas. Sendo assim, são necessários métodos heurísticos de otimização de CLCs.

Figura 6 – Saída S do Circuito Somador Completo projetada pela soma de produtos.

Fonte: Figura produzida pelo autor.

Figura 7 – Saída S do Circuito Somador Completo projetada pelo produto das somas.

Fonte: Figura produzida pelo autor.

## 4 APRENDIZADO POR REFORÇO

Os três paradigmas do aprendizado de máquina são o aprendizado supervisionado, o não supervisionado e o aprendizado por reforço (31). No aprendizado supervisionado, tenta-se predizer o valor de uma variável dependente a partir de uma lista de variáveis independentes. A base de dados nesse caso é rotulada. Com isso, é possível saber o erro do sistema para um conjunto de entradas e assim ajustar os valores de seus parâmetros de acordo com esse erro. Já no aprendizado não supervisionado, tenta-se estabelecer padrões dentro da base de dados. Esta por sua vez não possui rótulos e o aprendizado se dá estabelecendo relações e similaridades entre os parâmetros dos objetos ali contidos (31).

Já no aprendizado por reforço, tenta-se guiar um agente inteligente na tomada de decisões. As decisões são chamadas de políticas. O aprendizado ocorre à medida que o agente utiliza as políticas disponíveis: quando a política dá um bom resultado o agente é recompensado positivamente e quando a política dá um resultado ruim ele é punido, ou seja, é recompensado negativamente (35). Como o agente tende a escolher políticas de acordo com sua experiência, as políticas boas são reforçadas e passam a ser tomadas com cada vez mais frequência e, com isso, a eficácia do agente para aquela situação melhora com o passar do tempo.

#### 4.1 O PROBLEMA DO K-ARMED BANDITS E A ESTRATÉGIA $\epsilon$ -GREEDY

O problema do *K-armed Bandits*, ou caça níqueis de K-alavancas, é um problema alegórico que visa descrever uma situação onde um agente inteligente tem um conjunto definido de políticas para adotar. Cada política tendo uma recompensa média distinta, porém desconhecidas para o agente. Este deseja maximizar seus ganhos no final de um número finito, porém relativamente longo, de iterações (21).

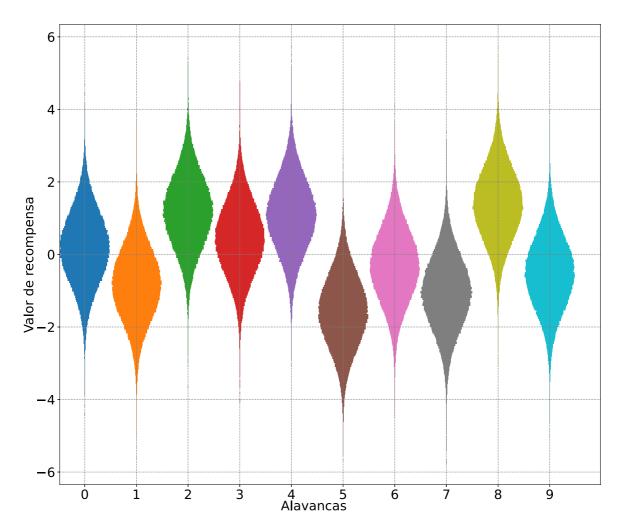

No K-armed Bandits um apostador se vê frente a uma máquina caça niqueis com diversas alavancas. Cada alavanca retorna valores de recompensa aleatórios, porém distribuídos em torno de uma média  $m_k$ , que varia de alavanca para alavanca. A Figura 8 é um exemplo da distribuição de recompensas de um caça níqueis de 10 alavancas, nela o zero representa a situação onde o apostador conseguiu o mesmo valor da ficha que colocou no caça-niqueis. Valores negativos ocorrem quando ele conseguiu prêmios menores do que o preço da ficha. Valores positivos, quando conseguiu valores maiores que o preço da ficha.

Figura 8 – Distribuição de recompensas das alavancas em um caça-níqueis em um problema do tipo k-armed bandits de 10 alavancas. Cada posição representa uma alavanca e sua distribuição de recompensas.

Fonte: Figura produzida pelo autor.

O apostador não sabe qual alavanca é a melhor e ele quer maximizar seus ganhos. À medida que ele usa as alavancas, ele calcula a média de recompensa que obteve por cada uma. Ele pode, portanto, adotar uma estratégia gulosa, puxando a alavanca na qual ele obteve melhor recompensa média até o momento. Apesar de ser uma estratégia aparentemente boa, é provável que o apostador gaste mais tentativas do que o necessário em uma alavanca que não é a melhor e, portanto, ele vai terminar suas jogadas com um ganho total menor do que poderia ter se tivesse localizado a melhor alavanca mais cedo.

Uma forma de se contornar esse problema é com a estratégia  $\epsilon$ -greedy ou  $\epsilon$ -gulosa. Por tal estratégia, existe uma probabilidade  $\epsilon$  do apostador ignorar a estratégia gulosa naquela jogada e puxar uma alavanca aleatória. Quando ele faz isso, ele está adotando um movimento exploratório e, portanto, aumentando as chances de encontrar a melhor

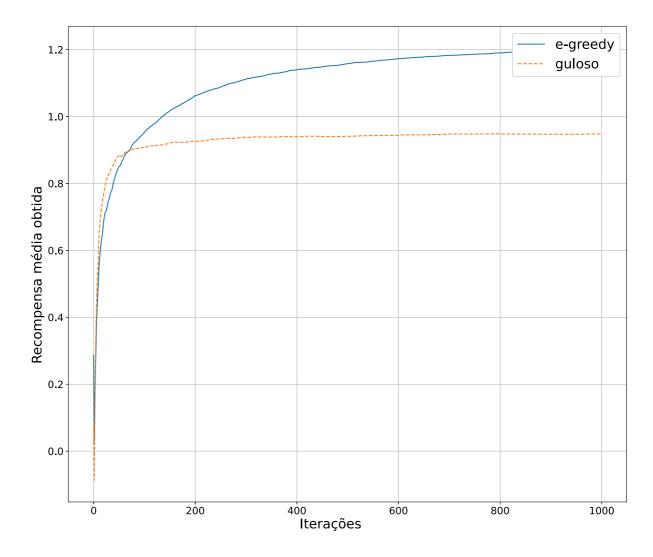

alavanca mais cedo e, com isso, ter um ganho final maior do que se tivesse adotado uma estratégia puramente gulosa. A Figura 9 mostra a comparação da eficácia dos apostadores usando a estratégia gulosa e com a estratégia  $\epsilon$ -greedy, com  $\epsilon=0.1$ . Onde o eixo das abscissas representa quantas vezes o apostador puxou uma alavanca e o das ordenadas o valor que ele obteve ao acionar a alavanca escolhida. Os valores representados no gráfico são a média de 200 jogos. É possível observar que a estratégia gulosa normalmente se estabiliza em uma alavanca com um valor bom de recompensa antes da estratégia  $\epsilon$ -greedy. No entanto, a estratégia  $\epsilon$ -greedy consegue encontrar um valor melhor de alavanca na maioria das vezes, conseguindo uma melhor média de recompensa por ativação do que a estratégia gulosa.

Figura 9 – Comparação dos valores médios de recompensa, por acionamento de alavanca, das estratégias gulosa e a  $\epsilon$ -greedy com  $\epsilon = 0.1$ .

Fonte: Figura produzida pelo autor.

Para se manter o registro da média de recompensa obtida por cada política, utiliza-se

a Equação da média dinâmica, definida por (35):

$$R_{i,t+1} = R_{i,t} + \frac{Q_{i,t} - R_{i,t}}{O_{i,t}} \tag{4.1}$$

onde  $R_{i,t}$  é a recompensa média obtida pela política i na iteração t,  $Q_{i,t}$  é o valor de recompensa obtido pela política i na iteração t, e  $O_{i,t}$  é o número de vezes que a política i foi tomada.

#### 4.1.1 Inicialização com valores otimistas

No problema clássico do *K-armed Bandits*, o apostador assume inicialmente que cada alavanca dá recompensa 0. Isto é, valor arbitrário que não é o pior nem o melhor, já que valores positivos e negativos de recompensa são possíveis. Independente do valor inicial assumido, a Equação 4.1 garante que a estimativa do apostador vai convergir para a recompensa média de cada alavanca (35), desde que haja iterações o suficiente.

O valor inicial influencia na velocidade de convergência. Valores iniciais muito ruins, como por exemplo as recompensas negativas no problema dos k-armed bandits, retardam a convergência, pois nas iterações iniciais, a tendência vai ser o agente tomar repetidamente as politicas com que teve contato. Cada política que ele não assumiu vai ter um valor de recompensa muito pior que as demais e só terá chance de ser tomada durante a fase exploratória.

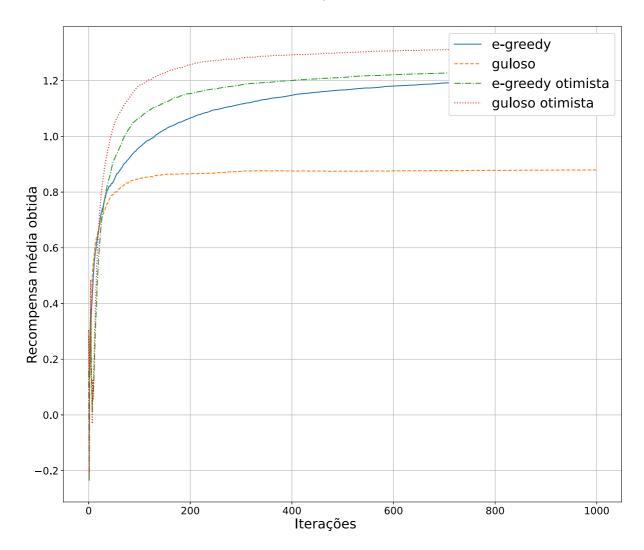

O oposto acontece quando se assume valores iniciais otimistas, como por exemplo recompensas altas no problema do k-armed bandits. Nesse caso, nas iterações iniciais, cada política que for tomada vai ter sua recompensa estimada como sendo pior que as demais. Isso força com que o agente alterne entre as políticas nas iterações iniciais, enquanto age com atitude gulosa. Esse comportamento vai se repetir até que as melhores políticas, que têm valores médios de recompensa mais próximos dos valores otimistas, se sobressaiam. A Figura 10 mostra a diferença entre a adoção de valores iniciais otimistas e não-otimistas para o problema com as alavancas da Figura 8.

Figura 10 – Comparação entre valor médio de recompensa média obtida por iteração entre a estratégia gulosa e a  $\epsilon$ -greedy e suas variações com inicialização de valores otimistas.  $\epsilon=0.1$

Fonte: Figura produzida pelo autor.

#### 4.1.2 Estratégia para problemas não estacionários

No caso de problemas de recompensa não estacionária, ou seja, naquele em que as recompensas das políticas se desviam de suas distribuições iniciais ao longo do tempo, a convergência do sistema devido à Equação 4.1 acaba sendo prejudicial ao sistema de aprendizagem. Nesta equação, não há diferença de peso entre as recompensas das ações tomadas mais recentemente das demais. Porém, as recompensas obtidas no passado referem-se às distribuições de recompensas que não são condizentes com as distribuições mais recentes. Ou seja, não ponderar os valores de recompensa de acordo com quão atual é a iteração favorece com que informação obsoleta influencie no sistema.

A solução para esse problema é manter um peso fixo para a diferença entre o valor

da recompensa ganha e a recompensa estimada (35). Essa mudança resulta na seguinte função de recompensa:

$$R_{i,t+1} = R_{i,t} + \alpha(Q_{i,t} - R_{i,t}) \tag{4.2}$$

onde  $\alpha \in [0,1]$  determina o peso que o valor de recompensa obtido  $(Q_{i,t})$  pela política i na iteração t tem no cálculo de estimativa de valor médio da recompensa da mesma. Um  $\alpha = 0$  inibe o aprendizado, uma vez que o valor médio estimado da recompensa não é atualizado, já  $\alpha = 1$  implica que o valor médio estimado da recompensa vai ser sempre igual o último valor de recompensa  $(Q_{i,t})$  obtido pela própria política i. Essa função de estimativa de recompensa média é não convergente e é isso que possibilita que o operador de aprendizado se adapte à mudança de valores médios das políticas (35).

# 5 PROGRAMAÇÃO GENÉTICA CARTESIANA

Proposta por Miller (27, 28), a Programação Genética Cartesiana é um método de programação genética onde os indivíduos são representados como um conjunto de nós dispostos em uma matriz. Cada nó tem uma função e entradas. Aplicadas ao projeto e otimização de CLCs, as funções são portas lógicas e o número de entradas varia de acordo com o tipo de porta, sendo geralmente duas.

Embora Miller assuma que a CGP possa trabalhar com ciclos, tradicionalmente um nó de uma determinada coluna só pode receber como entradas nós das colunas anteriores. Assim, o indivíduo da CGP pode ser visto como um digrafo acíclico. Outro atributo da CGP é o levelsback. Dado um nó na posição k, este pode ter os nós entre as posições k-levelsback e k-1 como suas entradas. Além disso, qualquer saída ou nó pode receber as entradas do sistema como sua entrada.

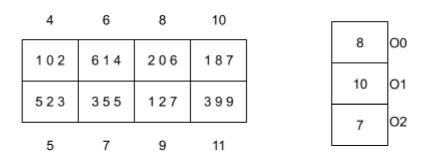

A Figura 11 ilustra a representação de uma solução da CGP. É possível observar que alguns nós não possuem caminho para uma das saídas do circuito. Esses nós, em cinza na figura, são chamados de nós inativos e não afetam o fenótipo, mas carregam informações evolutivas por deriva genética. A Figura 12 mostra o genótipo da solução candidata apresentada na Figura 11. Existem três valores em cada nó: os dois últimos são os nós de entrada e o primeiro valor representa uma função lógica. isto é mapeado como 1 sendo a função AND, 2 OR, 3 NOT, 5 NOR e 6 XOR.

Figura 11 – Representação de uma solução da CGP.

Fonte: Figura produzida pelo autor.

Figura 12 – Genótipo de uma solução da CGP.

Fonte: Figura produzida pelo autor.

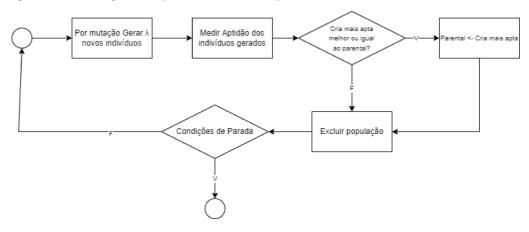

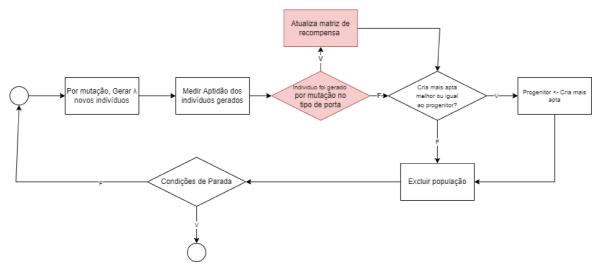

O Algoritmo 1 e a Figura 13 descrevem o processo de otimização de CLCs pela CGP. Neste a CGP é inicializada com uma população de  $\mu + \lambda$  indivíduos onde  $\mu$  é o número de progenitores e  $\lambda$  o número de filhos. É comum utilizar a configuração 1+4 na otimização de CLCs (8, 28) e, portanto, tal configuração é adotada neste trabalho. Dentro dessa população, o indivíduo mais apto é selecionado para ser o progenitor no começo do processo evolutivo. Durante o processo evolutivo o progenitor gera  $\lambda$  indivíduos por mutação e em seguida a função de aptidão é aplicada. Caso o individuo com melhor aptidão tenha a mesma aptidão que seu progenitor, o progenitor é sempre descartado. Esse processo se repete até que uma condição de fim seja alcançada.

Figura 13 – Diagrama que demonstra o processo evolutivo da CGP tradicional.

Fonte: Figura produzida pelo autor.

# 5.1 OPERADORES DE MUTAÇÃO

A CGP possui diferentes tipos de operadores de mutação. Será abordado nessa seção o operador Mutação Pontual, que é o operador inicialmente proposto para a CGP, e o Single Active Mutation (SAM), considerado o melhor operador dentre os comparados em (12).

# Algorithm 1 Programação Genética Cartesiana

```

1: procedure CGP(\mu, \lambda, população = [individuo 0, individuo 1, ..., individuo \mu + \lambda - 1

])

2:

Seleciona os melhores \mu indivíduos como progenitores e descarta os demais

3:

while Condições de parada não são alcançadas do

for i de 0 até \lambda do

4:

Realizar mutação em um progenitor P dentre os \mu progenitores para gerar

5:

novo individuo c_i

Seleciona os melhores \mu indivíduos como possíveis progenitores CP

6:

7:

for i de 0 até \mu do

Seleciona os \lambda + \mu melhores indivíduos da população como novos progenitores.

8:

Elimine os indivíduos da população, preservando apenas os progenitores P

9:

10:

Retorna o progenitor mais apto

```

A diferença entre esses operadores está em como estes selecionam quais nós sofrerão mutação. No tradicional Mutação Pontual (Algoritmo 2), uma quantidade pré-definida de nós é sorteada e então passam pelo processo de mutação. Não há garantias de que dentre os nós sorteados pela Mutação Pontual exista um nó ativo e portanto que o individuo criado por essa mutação seja fenotipicamente diferente de seu parental. Por esse motivo, circuitos com muitos nós inativos podem ser problemáticos para o operador de Mutação Pontual. Quanto mais nós inativos, maior a chance de apenas estes serem selecionados para a mutação e portanto gerar um indivíduo fenotipicamente idêntico ao progenitor. Isso diminui as chances de melhoria durante o processo evolutivo, uma vez que isso afeta negativamente a taxa de convergência para uma solução melhor na CGP.

## Algorithm 2 Operador de mutação pontual (PM)

```

procedure OPERADOR PM(Progenitor P, Quota de nós A)

CT = 0 ← Contador de nós que sofreram mutação

while CT < A do</li>

Escolha um nó aleatório em P

Escolha um elemento aleatório (entrada ou tipo de porta lógica)

Realize a mutação no elemento do nó escolhido

CT + +

```

O operador SAM (Algoritmo 3), por outro lado, repetidamente escolhe um nó aleatório, realiza a mutação neste e verifica se tal nó é ativo. Após um nó ativo ser modificado, o operador finaliza o processo de mutação no individuo. Isso faz com que, na maioria das vezes<sup>1</sup>. , o individuo gerado por tal tipo de mutação seja fenotipicamente

Do ponto de vista de estrutura do circuito, a SAM pode gerar um individuo fenotipicamente idêntico ao seu progenitor fazendo uma mutação redundante, como por exemplo trocar uma porta lógica por ela mesma. Do ponto de vista da tabela verdade/BDD do circuito, a SAM pode gerar indivíduos logicamente idênticos por diversos meios, como por exemplo quando uma das entradas do nó ativo modificado for uma tautologismo, ou uma contradição nesse caso algumas trocas de porta lógica podem resultar na mesma saída.

diferente do seu pai, o que favorece a taxa de convergência para uma solução melhor. A Figura 14 mostra o fluxo do operador PM e do operador SAM. É possível observar que a única diferença é a forma como cada operador define quando encerrar o processo de mutação nos nós de um individuo.

# **Algorithm 3** Operador SAM.

- 1: **procedure** OPERADOR SAM(Parental P)

- 2: **while** Nenhum nó ativo sofreu mutação **do**

- 3: Escolha um nó aleatório em P

- 4: Escolha um elemento aleatório (entrada ou tipo de porta lógica)

- 5: Realize a mutação no elemento do nó escolhido

Figura 14 – Diagrama demonstrando o operador de mutação pontual (PM) em comparação com o operador *Single Active Mutation* (SAM). Apenas a forma de decidir quando parar de realizar as mutações muda.

Fonte: Figura produzida pelo autor.

A mutação nos nós, começa com o operador escolhendo aleatoriamente qual elemento do nó será modificado. No caso da CGP aplicada à CLCs, os elementos são, entradas do nó e sua porta lógica. Caso uma das entradas seja selecionada, ela pode ser modificada para ser qualquer outro nó dentro do limite estabelecido pelo *levelsback* configurado no início da execução da CGP. Caso seja a porta lógica, o operador vai trocar a porta atual por qualquer porta dentro do conjunto de portas possíveis do problema. Todas essas escolhas são feitas de forma não enviesada e com distribuição de probabilidade constante entre os elementos possíveis. A Figura 15 representa esse processo.

Sorteia qual elemento do nó vai ser modificado

Realiza mutação do tipo de porta

Realiza mutação na primeira entrada

Realiza mutação na segunda entrada

Figura 15 – Diagrama demonstrando o processo de mutação em um nó da CGP

# 6 MÉTODO PROPOSTO

Ao longo desse estudo, dois métodos foram propostos: a CGP-RL (33) e a Node CGP-RL (32). Ambos os métodos envolvem um operador de mutação adaptativo que usa a estratégia  $\epsilon$ -greedy para enviesar a mutação das portas lógicas (CGP-RL) ou dos elementos do nó (Node CGP-RL). Neste capítulo, ambos os métodos são explicados detalhadamente.

## 6.1 CGP-RL

No trabalho (7), foi sugerida uma matriz de prioridade de trocas de portas lógicas pelo operador de mutação da CGP. Tal operador funciona da seguinte forma: Ao realizar a mutação no tipo de porta lógica de um nó, o operador consulta uma matriz, tal qual na Figura 16 com um peso de enviesamento para trocas que tem maior chance de resultarem em um melhor individuo. O operador então acessa a linha dessa matriz correspondente ao tipo de porta lógica atual do nó. Cada coluna corresponde a um tipo de porta lógica e os valores de cada célula na linha acessada correspondem as chances da troca da porta lógica atual do nó pela porta correspondente daquela coluna gerar um melhor individuo. Esses valores são convertidos em um aumento ou diminuição da probabilidade daquela troca ocorrer. Em (7) as matrizes tem valores fixos aos quais os autores chegaram após observação do comportamento da CGP em diversos problemas.

Figura 16 – Matrizes de enviesamento de mutação propostas em (7).

Fonte: SILVA et al., 2018.

O enviesamento proposto pelos autores conseguiu melhorar a convergência para uma solução factível, bem como minimizar a quantidade de portas lógicas nos problemas investigados. Se um operador de mutação com viés estático tem um bom desempenho, é razoável imaginar que um operador adaptativo pode ter um desempenho melhor.

A CGP-RL, como pode ser visto na Figura 17, trata a escolha das portas lógicas como um problema do tipo k-armed bandits, onde as alavancas são o tipo de troca a

ser executada, o operador de mutação é o apostador e a aptidão do individuo, neste caso factibilidade para o projeto e número de transistores para a otimização é o valor de recompensa obtida pela aposta (33). O método proposto usa a estratégia  $\epsilon$ -greedy para montar adaptativamente uma tabela de preferência de troca de portas lógicas e, assim, guiar o operador de mutação para as trocas que tem sido mais bem sucedidas e desestimular as piores trocas. Como pode ser visto no Algoritmo 4 e na Figura 18, esta começa com a inicialização de duas matrizes quadradas de tamanho N, onde N é o total de diferentes tipos de portas lógicas que estão sendo utilizadas para resolver aquele problema. Uma das matrizes é a matriz de recompensas médias estimadas (R), que é onde o valor estimado de recompensa das políticas vai estar armazenado. A outra matriz é a matriz de ocorrências (OM), que é onde fica o registro de quantas vezes cada política foi tomada. Em seguida, a população é inicializada da mesma forma que na CGP tradicional, como descrito no Capítulo 5. O algoritmo também é inicializado com uma taxa de exploração  $\epsilon$  que determina a probabilidade do operador de mutação escolher uma alternativa gulosa, ou adotar uma movimento exploratório.

Figura 17 – Relação da abordagem do problema de escolha de troca de portas lógicas pelo operador de mutação da CPG com o problema alegórico dos *k-armed bandits*.

Fonte: Figura produzida pelo autor.

A CGP-RL foi projetada para operar com a mutação SAM. Sendo assim, cada individuo é gerado por uma quantidade variável de mutações em nós inativos e apenas uma mutação, a última, em um nó ativo. Na CGP-RL, cada indivíduo carrega informações sobre essa mutação, ou seja, a mutação no nó ativo que o gerou. Depois que o parental gera  $\lambda$  filhos, a aptidão de cada individuo é medida. A aptidão depende do objetivo do processo evolutivo. No trabalho onde foi proposta, a distância de Hamming com relação ao circuito desejado foi usada para aptidão no processo de design de CLCs enquanto o total de transistores foi usada no processo de otimização de CLCs. Em ambos os casos o individuo mais apto é o que pontuava menor nas métricas utilizadas. A aptidão, junto com a informação sobre qual tipo de troca de porta ocorreu são usadas para atualizar a matriz de recompensas médias estimadas usando a Equação 4.1.

# Algorithm 4 CGP-RL

```

1: procedure CGP-RL(\lambda, \epsilon)

OM \leftarrow Matriz de ocorrências

R \leftarrow \text{Matriz de recompensas estimadas}

3:

while Condições de parada não alcançadas do

4:

for i de 0 até \lambda do

5:

Realizar mutação CGP-RL em P para gerar c_i, com taxa de exploração \epsilon

6:

for i de 0 até \lambda do

7:

if Indivíduo c_i foi criado por mutação no tipo de porta lógica then

8:

g \leftarrow tipo de porta lógica no nó ativo de P que sofreu mutação

9:

f \leftarrow \text{tipo de porta lógica resultante da mutação no nó de } c_i

10:

11:

OM_{p,f} + +

Atualiza R_{p,f}, considerando a aptidão de c_i de acordo com a Equação

12:

4.1

C_i \leftarrow \text{cria mais apta do progenitor } P

13:

if Aptid\tilde{a}o(C_i) é melhor ou igual a Aptid\tilde{a}o(P) then

14:

P \leftarrow C_i

15:

16:

Elimine os indivíduos da população, preservando apenas P

17: Retorna P

```

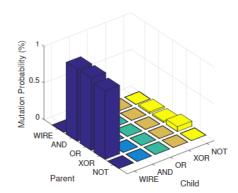

Figura 18 – Diagrama demonstrando o processo evolutivo da CGP-RL. A diferença com relação à CGP tradicional são os passos em vermelho, correspondentes à atualização da matriz de recompensas de troca de portas.

Fonte: Figura produzida pelo autor.

A atualização das matrizes ocorre da seguinte maneira: primeiramente é obtida a informação sobre a mutação que gerou o individuo e, apenas se essa mutação foi do tipo de porta, as matrizes são atualizadas. Então, usa-se o valor correspondente ao tipo da porta antes da mutação para acessar as linhas das matrizes e o valor depois da mutação para acessar as colunas. OM é atualizada primeiro, com um incremento na célula acessada. Cada troca de tipo de porta é uma política na CGP-RL, portanto, cada célula da OM

representa a quantidade de vezes que cada política foi tomada. A célula atualizada de OM entra na Equação 4.1 como  $O_{i,j}$  onde i é o valor do tipo de porta do parental, e j o valor do tipo de porta do filho. A aptidão do indivíduo entra como a recompensa obtida  $Q_{i,j}$ . R armazena os valores médios estimados de recompensa e, portanto,  $R_{i,j}$  vai ser a recompensa estimada para a política que gerou o individuo.

O operador de mutação funciona em conjunto com o SAM. Na mutação dos nós, primeiramente o operador sorteia qual elemento do nó vai ser modificado (primeira entrada, segunda entrada e porta lógica) de forma não enviesada. Caso a mutação seja nas entradas, ela é feita da mesma forma que na CGP tradicional, sem qualquer viés. Caso a mutação ocorra nas portas lógicas, existe uma probabilidade  $\epsilon$  do mesmo realizar um movimento de exploração e uma probabilidade de  $1-\epsilon$  dele realizar um movimento guloso, realizando sempre a troca onde obteve a melhor recompensa. No movimento exploratório a mutação da porta ocorre tal qual a CGP tradicional: a porta atual é trocada por uma outra porta sorteada de forma não enviesada. No movimento guloso, o operador de mutação acessa a linha da matriz R correspondente ao valor da porta a ser modificada e procura pelo menor valor da melhor recompensa naquela linha. Então, o operador troca a porta atual pela porta correspondente à coluna onde a melhor recompensa está. O operador ignora a diagonal principal da matriz de recompensas. Após a mutação do tipo de porta, independente do movimento realizado (exploratório ou guloso), o operador registra qual troca de porta foi realizada na criação do individuo. O Algoritmo 5 e descreve o operador de mutação da CGP-RL enquanto a Figura 19 representa a mutação do tipo de porta lógica em um nó.

# **Algorithm 5** Operador SAM CGP-RL

```

1: procedure OPERADOR SAM CGP-RL(Parental P, \epsilon)

2:

while Nenhum nó ativo sofreu mutação do

3:

Escolha um nó aleatório em P

Escolha um elemento aleatório (entradas ou tipo de porta lógica)

4:

if O elemento escolhido foi o tipo de porta lógica then

5:

g \leftarrow O tipo de porta lógica no nó sorteado

6:

V \leftarrow aleat\'{o}rio(0,1)

7:

if V \leq \epsilon then

8:

f \leftarrow porta lógica escolhida aleatoriamente

9:

10:

else

11:

R_q \leftarrow \text{Linha da matriz de } R \text{ referente à } g

f \leftarrow Porta lógica correspondente à coluna da primeira ocorrência do

12:

menor valor de R_g exceto coluna referente à g

Troque g por f

13:

Registre a troca de portas ocorrida

14:

else

15:

Realize a mutação da entrada sorteada de forma não enviesada

16:

```

Figura 19 – Mutação do tipo de porta lógica pela CGP-RL. O movimento exploratório se refere à mutação não enviesada da CGP tradicional. No movimento guloso a CGP-RL vai sempre executar a troca na qual há a melhor recompensa média obtida

#### 6.2 Node CGP-RL

A CGP-RL possui  $N^2-N$  políticas, onde N é o total de tipos de portas disponíveis para a solução do problema. A estimativa de recompensa das políticas é atualizada sempre que uma mutação do tipo de porta lógica acontece, o que corresponde a cerca de um terço das mutações durante o processo evolutivo. A escolha de qual elemento do nó sofrerá mutação, por outro lado, é uma tomada de decisão entre três políticas (realizar mutação na primeira entrada, segunda entrada e porta lógica) e a atualização da estimativa de recompensas ocorre sempre que um nó sofrer mutação. Tal tipo de mutação ocorre sempre.

Com menos politicas e uma frequência de aprendizado maior, um operador RL tem maiores chances de convergir mais rápido para a melhor política, desde que haja de fato alguma (35). Para determinar se há uma diferença entre as políticas de mutação de um nó que justifiquem o uso de um operador adaptativo, um estudo foi feito com base nos problemas classificados como pequenos em (8). A discussão sobre os experimentos realizados nesse estudo serão discutidos na Seção 7.1 do Capítulo 7.

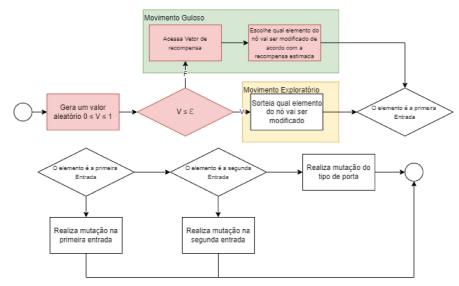

Os estudos levaram ao desenvolvimento da Node CGP-RL, uma versão da CGP cujo o operador de mutação tem viés adaptativo sobre qual elemento do nó vai sofrer mutação. A Node CGP-RL funciona de forma parecida com a CGP-RL. O Algoritmo 6 e a Figura 20 descrevem seu funcionamento. Inicialmente o vetor de recompensa média estimada (r) é inicializado. De acordo com os resultados de experimentos que serão vistos na seção 7.1, as políticas de mutação de um nó são de recompensa não estacionária.

# **Algorithm 6** Node CGP-RL

```

1: procedure Node CGP-RL(\lambda, \epsilon)

r \leftarrow \text{Vetor de recompensas estimadas}

while Condições de parada não alcançadas do

3:

for i de 0 até \lambda do

4:

Realizar mutação CGP-RL em P para gerar a c_i, tendo \epsilon como taxa de

5:

exploração

for i de 0 até \lambda do

6:

k \leftarrow \text{tipo de mutação no nó ativo que } P \text{ sofreu para gerar } c_i

7:

Atualiza r_k, considerando a aptidão de c_i de acordo com a Equação 4.2

8:

C_i \leftarrow \text{cria mais apta do parental } P

9:

if Aptid\tilde{a}o(C_i) É melhor ou igual a Aptid\tilde{a}o(P) then

10:

P \leftarrow C_i

11:

12:

Elimine os indivíduos da população, preservando apenas P

13: Retorna o parental P

```

Figura 20 – Diagrama demonstrando o processo evolutivo da *Node* CGP-RL. A diferença com relação à CGP tradicional é o passo em vermelho, correspondente à atualização do vetor de recompensas de troca de portas. A diferença com relação À CGP-RL é a ausência do desvio condicional para mutações do tipo de porta: Qualquer individuo que foi gerado por uma mutação em um nó ativo contribui para a atualização do vetor de recompensas.

Fonte: Figura produzida pelo autor.

A inicialização da população ocorre tal qual na CGP tradicional e então o processo evolutivo é iniciado. Cada individuo gerado tem registrado o tipo de mutação que o gerou. Da mesma forma que na CGP-RL, a aptidão de cada individuo e sua informação de mutação são usadas para atualizar o valor recompensa média estimada nas políticas contidos no vetor r, conforme a Equação 4.2, onde  $Q_{i,t}$  é o valor de aptidão do individuo, gerado pela política de mutação i na iteração t,  $R_{i,t}$  é o valor estimado de recompensa média da política e  $0 \le \alpha \le 1$  é o peso dado para as informações mais recentes.

Durante o processo de mutação, para cada nó, o operador tem uma probabilidade  $\epsilon$  de executar um movimento exploratório e realizar a mutação de forma não enviesada.