# Universidade Federal de Juiz de Fora Programa de Pós-Graduação em Engenharia Elétrica

Igor Dias Neto de Souza

Controle Digital com Malha Dupla de Tensão Aplicado a um Conversor Formador de Rede

Dissertação de Mestrado

Juiz de Fora 2017

Igor Dias Neto de Souza

Controle Digital com Malha Dupla de Tensão Aplicado a um Conversor

Formador de Rede

Dissertação apresentada ao Programa de Pós graduação em Engenharia Elétrica, área de concentração: Sistemas Eletrônicos, da Faculdade de Engenharia da Universidade Federal de Juiz de Fora como requisito parcial para obtenção do grau de Mestre.

Orientador: Prof. Pedro Machado de Almeida, Dr. Eng.

Juiz de Fora

Ficha catalográfica elaborada através do programa de geração automática da Biblioteca Universitária da UFJF, com os dados fornecidos pelo(a) autor(a)

Souza, Igor Dias Neto de .

Controle Digital com Malha Dupla de Tensão Aplicado a um Conversor Formador de Rede / Igor Dias Neto de Souza. -- 2017. 106 p.

Orientador: Pedro Machado de Almeida Dissertação (mestrado acadêmico) - Universidade Federal de Juiz de Fora, Faculdade de Engenharia. Programa de Pós Graduação em Engenharia Elétrica, 2017.

- 1. Power-Hardware-in-the-Loop. 2. Conversor emulador de rede.

- 3. Controle de tensão. 4. Amortecimento ativo. 5. Controlador ressonante digital modificado. I. Almeida, Pedro Machado de , orient. II. Título.

### Igor Dias Neto de Souza

# Controle Digital com Malha Dupla de Tensão Aplicado a um Conversor Formador de Rede

Dissertação apresentada ao Programa de Pós graduação em Engenharia Elétrica, área de concentração: Sistemas Eletrônicos, da Faculdade de Engenharia da Universidade Federal de Juiz de Fora como requisito parcial para obtenção do grau de Mestre.

Aprovada em 17 de Fevereiro de 2017.

### BANCA EXAMINADORA:

### Prof. Pedro Machado de Almeida, Dr. Eng.

Universidade Federal de Juiz de Fora, UFJF

Orientador

### Prof. Pedro Gomes Barbora, D. Sc.

Universidade Federal de Juiz de Fora, UFJF

### Prof. André Augusto Ferreira, Dr.

Universidade Federal de Juiz de Fora, UFJF

Prof. Márcio do Carmo Barbosa Poncilio Rodrigues, Dr. Eng.

Instituto Federal Sudeste de Minas Gerais, IF Sudeste MG

### **AGRADECIMENTOS**

À Deus, meu primeiro agradecimento, que sempre está comigo e que tem me amparado até aqui.

Aos meus familiares, em especial meus pais, Marcos e Denise, aos meus irmãos Iago e Isadora e à minha avó Inês, por todo amor, paciência, suporte, motivação e confiança.

À Natália pelo profundo carinho, amor e cumplicidade que compartilhamos juntos, e pela capacidade de tornar meus dias mais felizes e completos.

Ao meu orientador e amigo, Pedro Machado de Almeida, pelos ensinamentos compartilhados, e principalmente pela ajuda durante o decorrer do trabalho. Além disso, agradeço também pela disponibilidade e pela esperança depositada em mim.

Ao meu coorientador, Pedro Gomes Barbosa, pelos conselhos e por sua disposição e boa vontade em ajudar ao longo do desenvolvimento do trabalho.

Ao amigo Gabriel Azevedo Fogli, pela profícua ajuda na montagem do protótipo e na programação do DSP. Agradeço ainda, os ensinamentos passados durante os anos de convivência no NAEP.

Ao amigo Rodolfo Lacerda pelas orientações referente à programação do DSP e por sempre estar disposto a ajudar.

Aos amigos do NAEP e LAPTEL: Andrei, Israel, Frederico, Pablo, Samuel, Henrique, Leandro Manso e Dayane.

Aos demais amigos que de certa forma me apoiaram.

À CAPES, à Universidade Federal de Juiz de Fora e ao Programa do Pós de Graduação em Engenharia Elétrica pela estrutura necessária ao desenvolvimento deste trabalho.

"O êxito da vida não se mede pelo caminho que você conquistou, mas sim pelas dificuldades que superou no caminho."

Abraham Lincoln

#### **RESUMO**

Esta dissertação apresenta um estudo de um conversor emulador de rede (CER) que faz parte de uma estrutura Power-Hardware-in-the-Loop (PHIL). O PHIL será futuramente utilizado para verificar os impactos causados pela integração de sistemas de geração fotovoltaico (PV) à rede elétrica, assim como a operação do sistema PV frente a distúrbios na rede. O CER, composto por um conversor fonte de tensão (VSC) de dois níveis e filtro de saída LC, é responsável por alimentar cargas isoladas emulando uma rede elétrica. A modelagem do conversor emulador de rede é feita no sistema de coordenadas estacionário  $(\alpha\beta0)$ , fornecendo um sistema de equações diferenciais usado para descrever o comportamento dinâmico do sistema. O conversor é controlado no modo de tensão, através da estratégia de modulação vetorial. Duas malhas de controle em cascata são projetadas. A malha interna utiliza compensadores em avanço digitais para amortecer a ressonância do filtro LC sem a necessidade de uma realimentação interna de corrente. Já a externa utiliza controladores ressonantes digitais modificados para rejeitar distúrbios harmônicos e garantir a qualidade da forma de onda da tensão no ponto de acoplamento comum. Os controladores ressonantes são conectados em série e o projeto é baseado no amortecimento dos zeros. Resultados experimentais, obtidos com o protótipo de laboratório, cujos controladores foram implementados em um processador digital de sinais TMS320F28335 da Texas Instruments, são usados para validar as estratégias de controle propostas.

Palavras-chave: Power-Hardware-in-the-Loop, conversor emulador de rede, controle digital, controle de tensão, filtro LC, amortecimento ativo, controlador ressonante digital modificado.

### ABSTRACT

This dissertation presents a study on a grid-former converter (GFC) which is a part of a Power-Hardware-in-the-Loop (PHIL) structure. The PHIL will be used to verify the impacts caused by the integration of photovoltaic (PV) generation systems into grid, as well as to study the PV operation under grid disturbances. The GFC, composed by a two-level voltage source converter with a LC output filter, is responsible to feed isolated loads emulating an electrical grid. The modeling of the grid-former converter is done in the stationary frame  $(\alpha\beta 0)$ , providing a set of differential equations that describes the dynamical behavior of the system. The converter is controlled in voltage mode by means of the space vector modulation (SVM) strategy. Two control loops are designed to control the static converter. At the inner loop a novel discrete-time active damping technique is proposed in order to damp the filter resonance without the need of current feedback. The method is based on an inner feedback loop with digital lead compensator on the feedback path while the external loop uses a discretetime integrator and a modified digital resonant controller to guarantee a decreasing frequency response and ensure the quality of the voltage waveform at the point of common coupling, respectively. The resonant controllers are connected in series and the design is based on its zeros damping. Experimental results obtained with the prototype, which controllers were implemented in a Texas Instruments TMS320F28335 are used to validate the proposed control strategies.

Keywords: Power-Hardware-in-the-Loop, grid-former converter, digital control, LC filter, active damping, modified digital resonant controller.

# LISTA DE ILUSTRAÇÕES

| Figura 1  | Estrutura básica de um PHIL.                                                                                                                | 31 |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 2  | Estrutura PHIL conectado a um sistema PV.                                                                                                   | 34 |

| Figura 3  | Conversor emulador de rede.                                                                                                                 | 36 |

| Figura 4  | Estrutura básica de um VSC com filtro de saída LC alimentando cargas locais                                                                 | 40 |

| Figura 5  | Controle da tensão de saída utilizando a corrente no capacitor na realimentação interna.                                                    | 42 |

| Figura 6  | Controle da tensão de saída utilizando a corrente no indutor na realimentação interna.                                                      | 42 |

| Figura 7  | Controle da tensão de saída utilizando a corrente no indutor e corrente na carga.                                                           | 43 |

| Figura 8  | Diagrama de bode das impedâncias de saída para dois tipos de contro-<br>ladores, considerando $G_R(s)=1$                                    | 45 |

| Figura 9  | Estratégia de controle de um conversor fonte de tensão (do inglês, <i>Voltage Source Converter</i> ) (VSC) utilizando uma malha de controle | 47 |

| Figura 10 | Estratégia de controle de um VSC utilizando duas malhas de controle.                                                                        | 47 |

| Figura 11 | Respostas em frequência do controlador de corrente para diferentes ganhos.                                                                  | 48 |

| Figura 12 | Diagrama de um conversor fonte de tensão trifásico.                                                                                         | 50 |

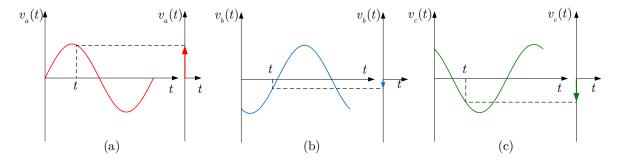

| Figura 13 | Componentes instantâneas: (a) fase a, (b) fase b, (c) fase c                                                                                | 51 |

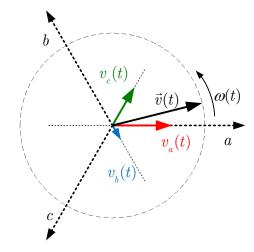

| Figura 14 | Representação do vetor espacial de tensão nos sistemas de coordenadas $(abc)$ .                                                             | 51 |

| Figura 15 | Representação gráfica do vetor espacial de tensão nos sistemas de co-                                                                       |    |

|           | ordenadas $(\alpha\beta 0)$ .                                                                               | 52 |

|-----------|-------------------------------------------------------------------------------------------------------------|----|

| Figura 16 | Equivalente monofásico do conversor emulador de rede (CER)                                                  | 52 |

| Figura 17 | Representação em diagrama de blocos do sistema.                                                             | 56 |

| Figura 18 | Diagrama de blocos da estratégia do amortecimento ativo no tempo contínuo.                                  | 61 |

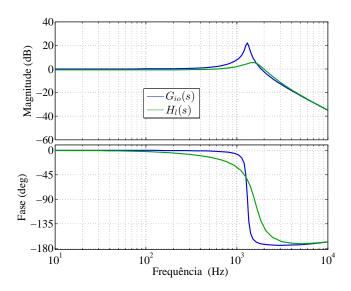

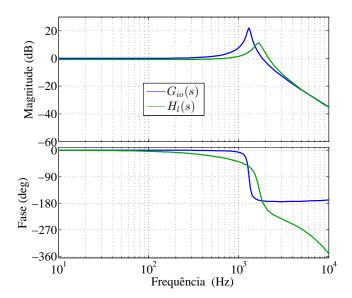

| Figura 19 | Diagrama de Bode de $G_{io}(s)$ e $H_l(s)$                                                                  | 62 |

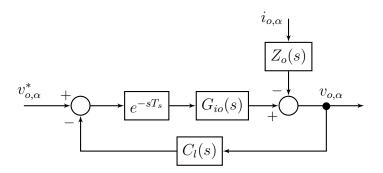

| Figura 20 | Diagrama de blocos da estratégia do amortecimento ativo no tempo contínuo com atraso de amostragem.         | 63 |

| Figura 21 | Diagrama de bode de $G_{io}(s)$ e $H_l(s)$ com atraso de amostragem                                         | 64 |

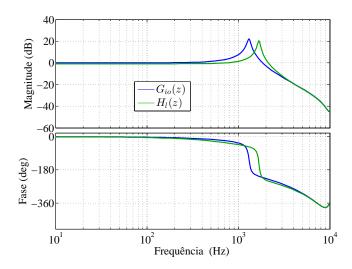

| Figura 22 | Diagrama de bode de $G_{io}(z)$ e $H_l(z)$ com atraso de amostragem                                         | 64 |

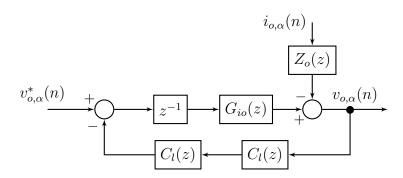

| Figura 23 | Diagrama de blocos da estratégia de amortecimento ativo no tempo discreto.                                  | 65 |

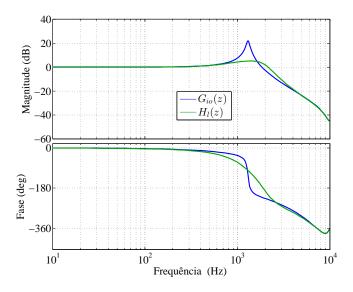

| Figura 24 | Diagrama de bode de $G_{io}(z)$ e $H_l(z)$ .                                                                | 66 |

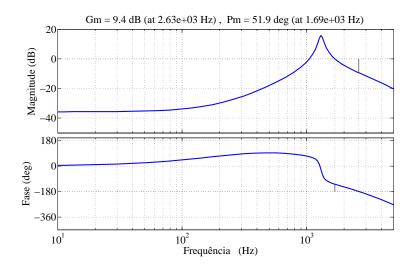

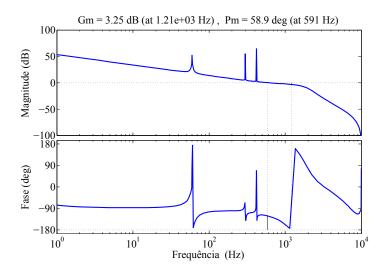

| Figura 25 | Diagrama de bode da função de transferência para a malha interna em malha aberta.                           | 67 |

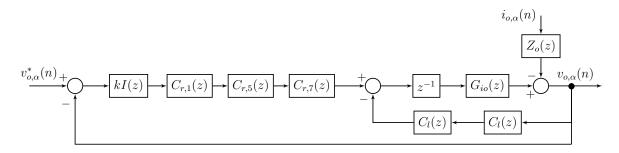

| Figura 26 | Diagrama de blocos do controle completo.                                                                    | 67 |

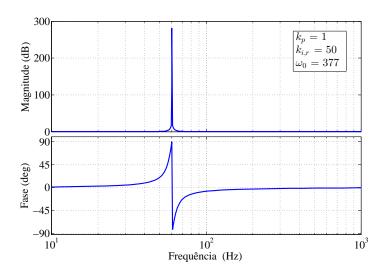

| Figura 27 | Resposta em frequência do controlador ressonante ideal                                                      | 68 |

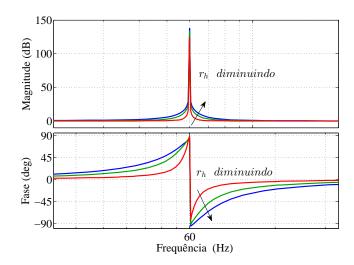

| Figura 28 | Diagrama de bode do controlador ressonante para diferentes valores de $r_h$ .                               | 70 |

| Figura 29 | Diagrama de bode da função de transferência para o sistema em malha aberta.                                 | 72 |

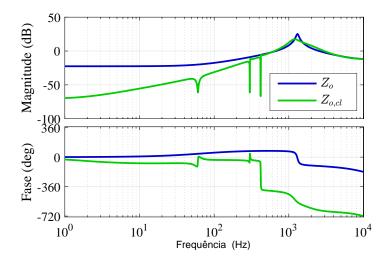

| Figura 30 | Diagrama de bode da impedância de saída: malha aberta $(Z_o)$ e malha fechada $(Z_{o,cl})$ .                | 72 |

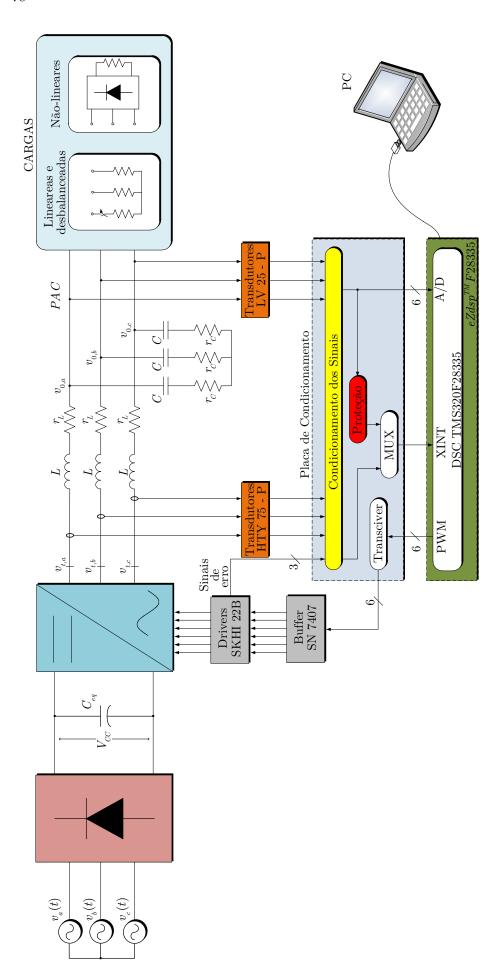

| Figura 31 | Esquema do sistema experimental implementado em laboratório                                                 | 78 |

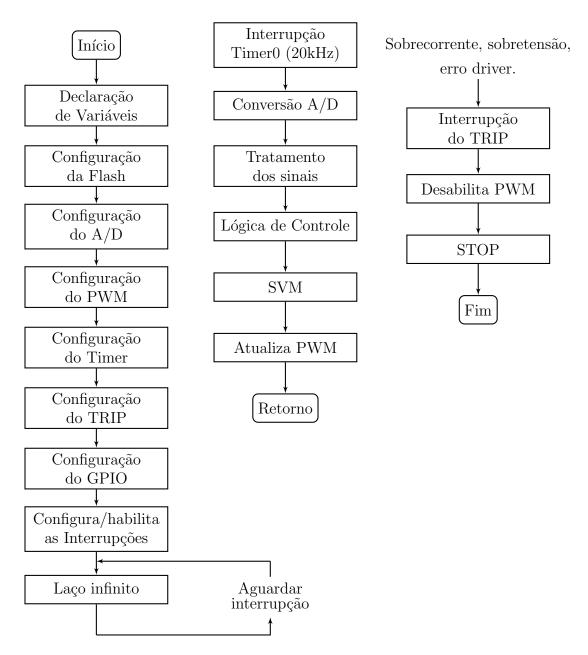

| Figura 32 | Fluxograma do algoritmo implementado no TMS320F28335                                                        | 81 |

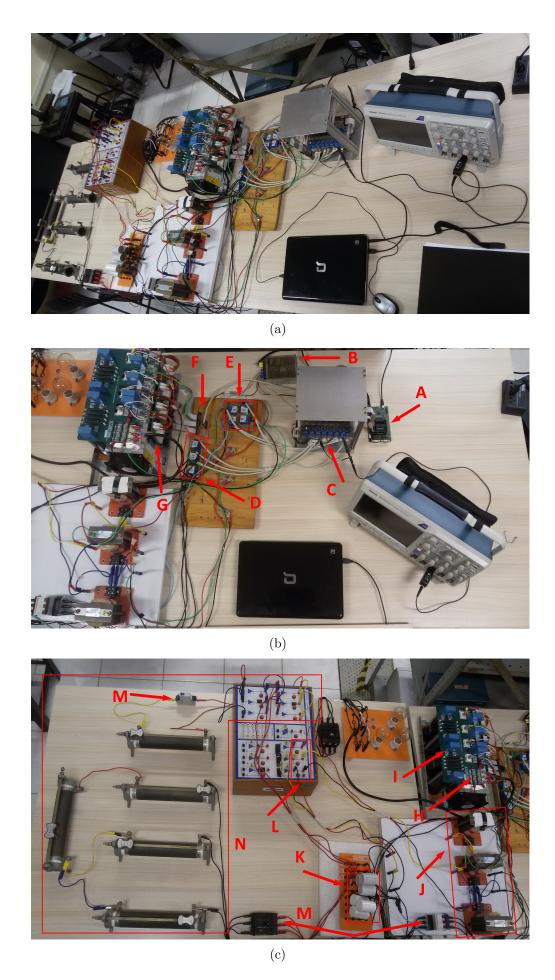

| Figura 33 | Imagem da estrutura utilizada: (a) Bancada experimental; (b) Circuito de controle; (c) Circuito de potência | 83 |

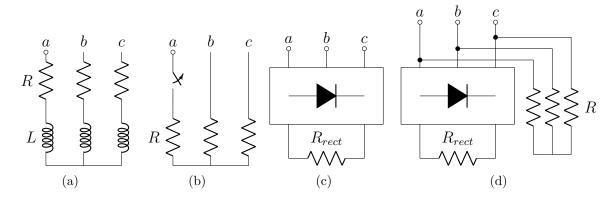

| Figura 34 | Cargas testadas no conversor emulador de rede: (a) Carga RL trifásica e equilibrada; (b) Carga resistiva bifásica; (c) Retificador trifásico não controlado com carga resistiva; (d) Carga resistiva trifásica balanceada e retificador trifásico não controlado. | 84 |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

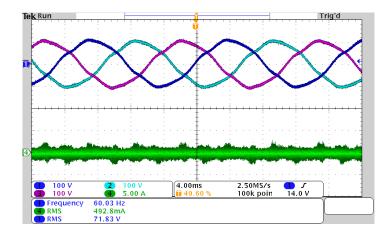

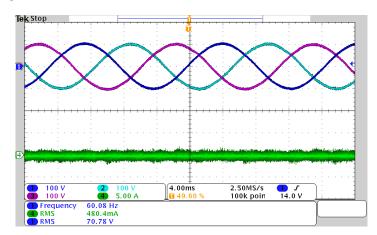

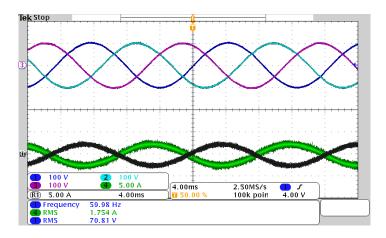

| Figura 35 | Formas de onda das tensões trifásicas no ponto de acoplamento comum (PAC) e corrente na carga.                                                                                                                                                                    | 85 |

| Figura 36 | Espectro de frequência da tensão de uma das fases no PAC sem conexão de carga.                                                                                                                                                                                    | 86 |

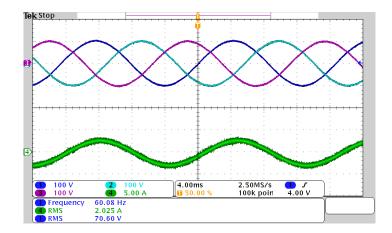

| Figura 37 | Formas de onda das tensões trifásicas no PAC com compensação de harmônicos.                                                                                                                                                                                       | 86 |

| Figura 38 | Formas de onda das tensões trifásicas no PAC e a corrente da carga na "fase b" para uma carga RL equilibrada.                                                                                                                                                     | 87 |

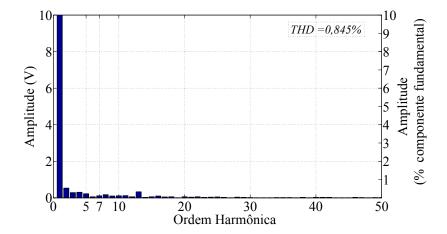

| Figura 39 | Espectro de frequência da tensão de uma das fases no PAC para uma carga RL equilibrada, THD = $0.845\%$                                                                                                                                                           | 87 |

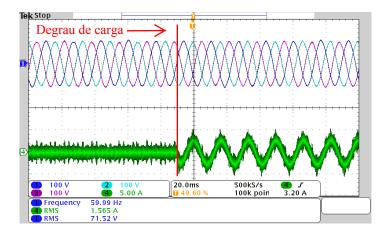

| Figura 40 | Forma de onda das tensões trifásicas no PAC frente a degrau de carga.                                                                                                                                                                                             | 88 |

| Figura 41 | Formas de onda das tensões trifásicas no PAC e a corrente de saída para uma carga resistiva desequilibrada conectada entre as fases "c" e "b".                                                                                                                    | 88 |

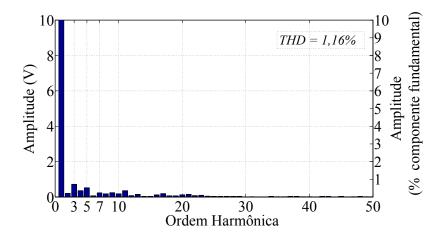

| Figura 42 | Espectro de frequência da tensão de uma das fases no PAC para uma carga resistiva desequilibrada, THD = $1,16\%$                                                                                                                                                  | 89 |

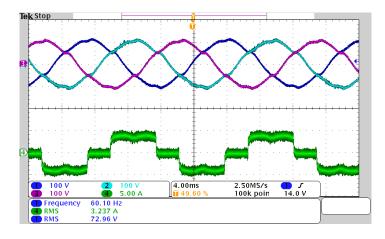

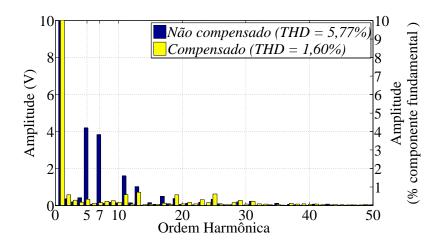

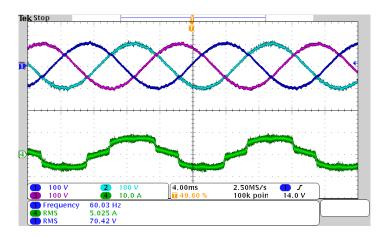

| Figura 43 | Formas de onda da tensão de saída trifásica e corrente de carga, sem compensação harmônica, para uma ponte retificadora a diodo usado como carga, THD = $5,77\%$ .                                                                                                | 89 |

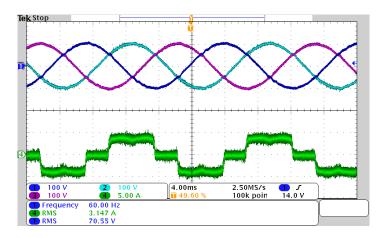

| Figura 44 | Formas de onda da tensão de saída trifásica e corrente de carga, com compensação harmônica, para uma ponte retificadora a diodo usado como carga, THD=1,60%.                                                                                                      | 90 |

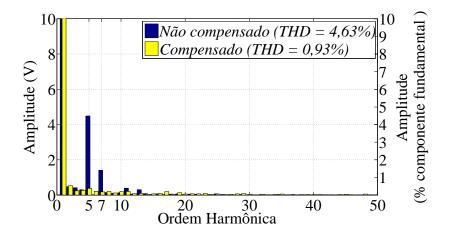

| Figura 45 | Espectro harmônico da tensão de saída para um retificador trifásico não controlado usado como carga.                                                                                                                                                              | 90 |

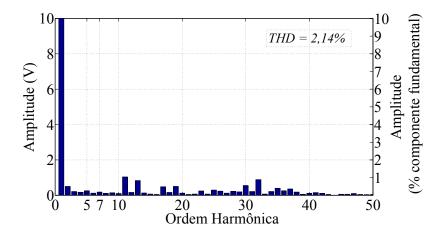

| Figura 46 | Formas de onda das tensões trifásicas no PAC e a corrente de saída para                                                                                                                                                                                           |    |

|           | uma carga resistiva equilibrada e uma ponte retificadora a diodos 91                                                                        |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Figura 47 | Espectro harmônico da tensão de saída de uma das fases para uma carga resistiva equilibrada e uma ponte retificadora a diodos, THD = 2,14%. |

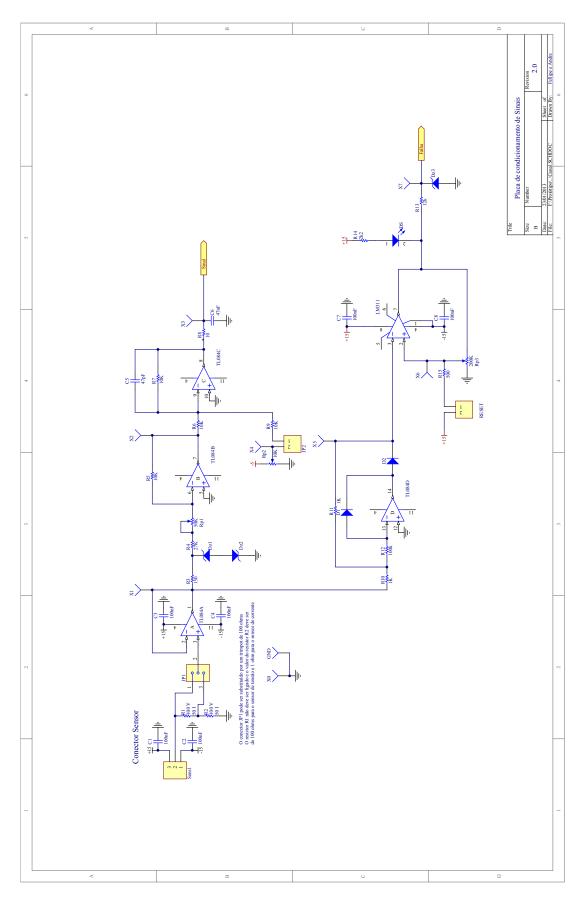

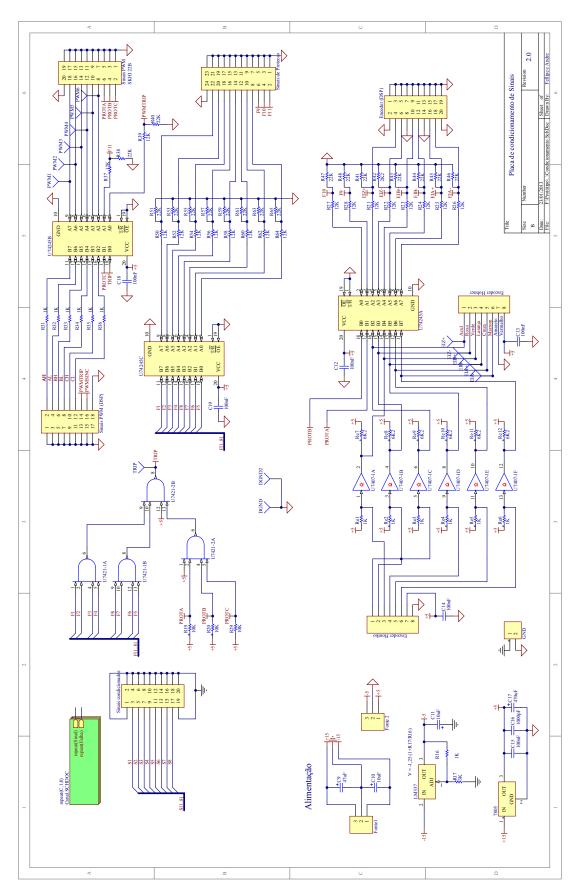

| Figura 48 | Circuito para condicionamento e proteção dos canais de tensão e corrente                                                                    |

| Figura 49 | Esquema da placa de condicionamento de sinais                                                                                               |

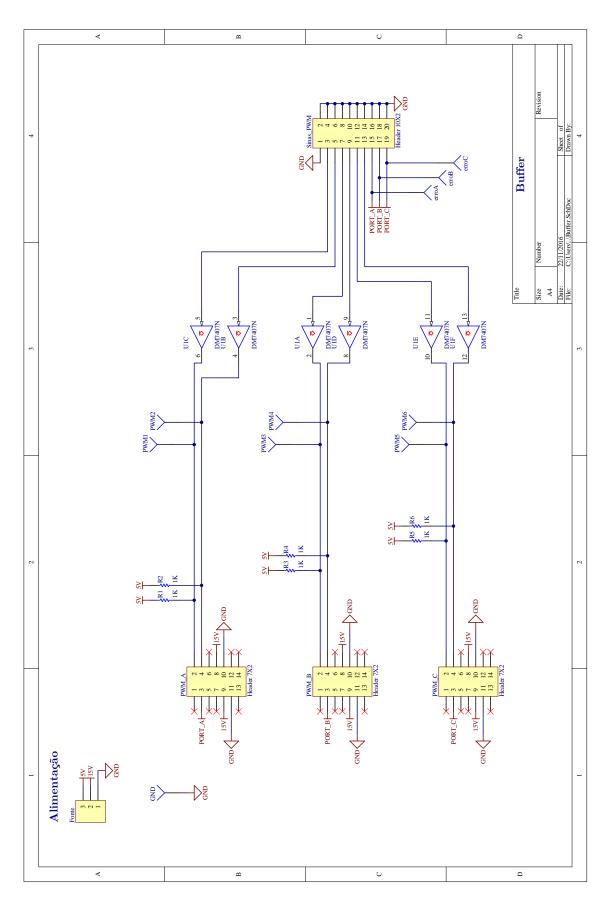

| Figura 50 | Esquema do buffer coletor aberto                                                                                                            |

### LISTA DE TABELAS

| Tabela 1 | Parâmetros do Sistema.                         | 58 |

|----------|------------------------------------------------|----|

| Tabela 2 | Parâmetros do Controlador.                     | 71 |

| Tabela 3 | Características do transdutor de tensão.       | 77 |

| Tabela 4 | Características do transdutor de corrente.     | 79 |

| Tabela 5 | Características do driver SKHI22B da Semikron. | 80 |

| Tabela 6 | Parâmetros das Cargas.                         | 84 |

### LISTA DE ABREVIATURAS E SIGLAS

A/D analógico-digital

CA corrente alternada

CC corrente contínua

CHIL Control-Hardware-in-the-loop

CMC controle modo de corrente (do inglês, current-mode control)

CER conversor emulador de rede

D/A digital-analógico

**DB** deadbeat

DSC controlador digital de sinais (do inglês, Digital Signal Controller)

**DSP** processador digital de sinais (do inglês, Digital Signal Processor)

**FLC** controle por linearização da realimentação (do inglês, *Feedback Linearization Control*)

**FOH** First-order holder

**GPIO** portas de propósito geral (do inglês, (General Purpose Input Output))

**HIL** Hardware-in-the-loop

**HUT** hardware sob teste

**HVDC** high-voltage direct current

I/O entrada e saída (do inglês, input-output)

**IGBT** Transistor Bipolar com Gatilho Isolado (do inglês, *Insulated Gate Bipolar Transistor*)

NAEP Núcleo de Automação e Eletrônica de Potência

PAC ponto de acoplamento comum

PHIL Power-Hardware-in-the-loop

PI proporcional-integrador

PID proporcional-integral e derivativo

PR proporcional-ressonante

PV célula fotovoltaica (do inglês, *Photovoltaic cell*)

PWM modulação por largura de pulso (do inglês, Pulse Width Modulation)

RTDS Real Time Digital Simulator

SEP sistema elétrico de potência

SMC controle por modos deslizantes (do inglês, sliding mode control)

**SVM** modulação vetorial (do inglês, Space Vector Modulation)

THD distorção harmônica total (do inglês, Total Harmonic Distortion)

TNA transient network analyzer

UFJF Universidade Federal de Juiz de fora

**UPS** fonte ininterrupta de energia (do inglês, *Uninterruptible Power Supply*)

VMC controle modo de tensão (do inglês, voltage-mode control)

VSC conversor fonte de tensão (do inglês, Voltage Source Converter)

**ZOH** Zero-order holder

# SUMÁRIO

| 1 I   | ntrodução                                                                       | 29 |

|-------|---------------------------------------------------------------------------------|----|

| 1.1   | Power-Hardware-in-the-Loop                                                      | 31 |

| 1.2   | Identificação do problema                                                       | 32 |

| 1.3   | Motivação do trabalho                                                           | 34 |

| 1.4   | Objetivos                                                                       | 35 |

| 1.5   | Estrutura do Trabalho                                                           | 37 |

|       | Revisão de Controladores de Tensão para Conversores Estáticos com<br>Filtros LC | 39 |

| 2.1   | Introdução                                                                      | 39 |

| 2.2   | Estratégias de controle aplicadas a conversores VSC com filtro LC               | 39 |

| 2.3   | Ressonância dos Filtros LC                                                      | 45 |

| 2.3.1 | Amortecimento Passivo                                                           | 46 |

| 2.3.2 | 2 Amortecimento Ativo                                                           | 46 |

| 2.4   | Conclusões Parciais                                                             | 48 |

| 3 I   | Fundamentos Teóricos                                                            | 49 |

| 3.1   | Introdução                                                                      | 49 |

| 3.2   | Funcionamento Básico do Conversor Fonte de Tensão Trifásico                     | 49 |

| 3.3   | O Vetor Espacial                                                                | 50 |

| 3.4   | Modelagem do Conversor Emulador de Rede                                         | 51 |

| 3.5   | Representação no Espaço de Estados                                              | 54 |

| 3.5.1 | Discretização                                                                   | 57 |

| 3.6   | Conclusões Parcias                                                              | 58 |

| 4 Estratégia de Controle                                             | 61   |

|----------------------------------------------------------------------|------|

| 4.1 Introdução                                                       | 61   |

| 4.2 Amortecimento Ativo - Malha interna de Tensão                    | 61   |

| 4.2.1 Projeto dos Compensadores por Avanço de Fase no Tempo Contínuo | 62   |

| 4.2.2 Projeto dos Compensadores por Avanço de Fase no Tempo Discreto | 65   |

| 4.3 Controle da malha externa de tensão                              | 67   |

| 4.3.1 Controlador Proporcional Ressonante                            | 68   |

| 4.3.2 Projeto de Controladores Ressonantes no Tempo Discreto         | 69   |

| 4.3.3 Estrutura Completa de Controle                                 | 70   |

| 4.4 Conclusões Parciais                                              | . 72 |

| 5 Resultados Experimentais                                           | 75   |

| 5.1 Introdução                                                       | . 75 |

| 5.2 Características do DSC Utilizado                                 | . 75 |

| 5.3 Características do Conversor Utilizado                           | . 76 |

| 5.4 Interface entre o Conversor e o DSC                              | . 76 |

| 5.4.1 Medição das grandezas Elétricas                                | . 77 |

| 5.4.2 Circuito de Condicionamento de Sinais Analógicos               | . 79 |

| 5.4.3 Disparo dos Interruptores                                      | . 79 |

| 5.5 Programação do DSC                                               | . 80 |

| 5.6 Bancada Experimental                                             | . 82 |

| 5.7 Validação Experimental                                           | . 84 |

| 5.7.1 Caso 1                                                         | . 85 |

| 5.7.2 Caso 2                                                         | . 86 |

| 5.7.3 Caso 3                                                         | . 88 |

| 5.7.4 Caso 4                                                         | . 89 |

| 5.7.5 Caso 5                                                         | . 90 |

| 5.8 Conclusões Parciais                                  | 91  |

|----------------------------------------------------------|-----|

| 6 Conclusões                                             | 93  |

| 6.1 Produção Científica Resultante Desta Pesquisa        | 95  |

| 6.2 Trabalhos Futuros                                    | 95  |

| Referências                                              | 97  |

| Apêndice A - Condicionamento dos sinais analógicos e PWM | 103 |

## 1 INTRODUÇÃO

Antes do surgimento dos primeiros simuladores digitais em tempo real (Real Time Digital Simulator (RTDS)), as simulações em tempo real dos sistemas de potência eram executadas utilizando modelos analógicos em escala reduzida, que geravam imprecisões e incertezas nas análises (FORSYTH; MAGUIRE & KUFFEL, 2004). Posteriormente, estas simulações foram realizadas através do transient network analyzer (TNA). O TNA é composto por uma coleção de modelos usados para estudar e simular os efeitos de possíveis surtos em um sistema de potência (PRATICO & EITZMANN, 1994). Estes dispositivos eram mais precisos que os modelos analógicos embora sejam mais custosos.

Simulação digital em tempo real de um sistema elétrico é a reprodução das formas de onda de saída (tensão/corrente), com a precisão desejada, que seja representativa do comportamento do sistema de potência real que está sendo modelado. Para atingir esse objetivo, o simulador em tempo real precisa resolver as equações do modelo matemático em um passo de simulação dentro do mesmo período no relógio do mundo real. Se o tempo de execução da simulação é menor ou igual ao passo de simulação escolhido, a simulação é considerada em tempo real. Caso contrário é considerada offline (IEEE PES Task Force on Real-Time Simulation of Power and Energy Systems, 2015). O passo de uma simulação em tempo real deve ser sincronizada com um relógio do mundo real, uma vez que o hardware do mundo real deve interagir com a simulação (PARK et al., 2013).

Um simulador em tempo real deve resolver um modelo em larga escala de rede elétrica de distribuição em até 50  $\mu$ s para que seja possível reproduzir o transitório de maneira fiel. Este é o tempo necessário para uma resolução adequada em sistemas de potência que operam em 50/60 Hz. Por outro lado, em sistemas com conversores eletrônicos de potência comutados, passos de simulação menores são requeridos. Se controlados digitalmente, circuitos chaveados em alta frequência podem operar em um microcontrolador com um clock interno com períodos de 1  $\mu$ s a 10 ns. Isto requer uma capacidade de processamento muito maior, aliada à habilidade de simulação com passos muito pequenos. Entretanto, apesar da dinâmica interna rápida dos conver-

sores estáticos, as interações a nível de sistema podem não requerer um passo muito pequeno (IEEE PES Task Force on Real-Time Simulation of Power and Energy Systems, 2015).

O primeiro simulador digital em tempo real comercial foi demonstrado pela RTDS Technologies Inc. em 1991. O RTDS é um simulador de sistemas de energia em tempo real, totalmente digital, desenvolvido no *Manitoba HVDC Research Centre* no final da década de 1980. O seu *hardware* é baseado em uma personalizada arquitetura de processamento paralela projetada especificamente para resolver o algoritmo de simulação de transitórios eletromagnéticos desenvolvido pelo Dr. Hermann Dommel (DOMMEL, 1969). O projeto é modular de modo que sistemas de potência de diferentes tamanhos possam ser acomodados em unidades, referidas como *racks*, ao simulador. Cada *rack* de *hardware* inclui cartões de comunicação e de processador ligados através de um plano comum (FORSYTH & KUFFEL, 2007). Além do RTDS existem outros simuladores em tempo real desenvolvidos pela *Typhoon HIL* e a *Opal Technologies*. Diferentemente do RTDS e do eMEGAsim desenvolvido pela *Opal*, o *Typhoon HIL* é voltado para simulação de conversores eletrônicos de potência.

A Operação em tempo real implica que um evento no sistema que dure, por exemplo, um segundo possa ser simulado em um segundo ou menos. As simulações digitais normalmente requerem muitos segundos ou minutos para executar os cálculos necessários e produzir uma solução para tal evento (KUFFEL et al., 1995). Uma alternativa para contornar este problema é utilizar a simulação *Hardware-in-the-loop* (HIL). De acordo com (TERLIP; KROPOSKI & MAKSIMOVIC, 2012) e (SANCHEZ; CASTRO & GARRIDO, 2012), na simulação HIL, parte do sistema é modelado e simulado em tempo real, enquanto que, o restante do sistema real é conectado a um circuito em malha fechada através de várias interfaces de entrada e saída (do inglês, *input-output*) (I/O), tais como conversores analógico-digital (A/D) e digital-analógico (D/A).

A simulação HIL pode ser de dois tipos: Control-Hardware-in-the-loop (CHIL) ou Power-Hardware-in-the-loop (PHIL). No CHIL, o sistema de potência juntamente com a eletrônica de potência são representados por um modelo no simulador em tempo real, enquanto o controlador digital, dispositivo sob teste, é conectado em malha fechada com o modelo. Por outro lado, na simulação PHIL, uma parte do sistema de potência é montado externamente ao simulador, exigindo um fluxo de potência, para o hardware externo, com amplitudes consideravelmente superiores àquelas do CHIL.

### 1.1 POWER-HARDWARE-IN-THE-LOOP

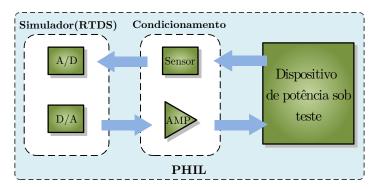

A tecnologia PHIL está se tornando cada vez mais popular em virtude da sua crescente utilização em simulações de sistemas elétricos de potência (SEP), eletrônica de potência, entre outros sistemas associados. O PHIL é baseado na combinação dos sinais de controle e medição do hardware sob teste (HUT) com a simulação em tempo real do restante do sistema. Simulação PHIL, como mostrado na Figura 1, refere-se aos casos em que um dispositivo de potência necessita ser testado. Neste cenário, o HUT absorve potência real enquanto o simulador lida com sinais digitais. Por este motivo, uma interface de tratamento é de suma importância para a adequação apropriada dos níveis das variáveis para o perfeito funcionamento do PHIL.

Figura 1: Estrutura básica de um PHIL.

Uma das principais contribuições desta tecnologia é fornecer um ambiente realista em que equipamentos reais, como por exemplo relés, possam ser testados antes de serem utilizados na prática. Como exemplo, algumas das potenciais aplicações do PHIL são em: (i) testes de máquinas elétricas como unidades de propulsão (STEURER et al., 2010) (FLEMING et al., 2009); (ii) geradores de turbina a gás como força motriz de navio elétrico (CHOE et al., 2014) (SIEGERS & SANTI, 2015) (LANGSTON et al., 2013) e (iii) gerenciamento (KERMANI et al., 2011) e armazenadores de energia (TRIGUI et al., 2009) de veículos elétricos híbridos. Além destes, o PHIL também está sendo amplamente utilizado em pesquisas com fontes alternativas de energia, tais como, solar (LIU et al., 2012) (JUNG et al., 2012) e eólica (HELMEDAG; ISERMANN & MONTI, 2014) (MäKINEN; MESSO & TUUSA, 2014), além de estudos em microrrede de corrente contínua (CC) (FANTAUZZI et al., 2015) e de corrente alternada (CA) (CROLLA et al., 2011). Os sistemas de transmissão high-voltage direct current (HVDC) também têm sido testados em plataformas de simulação em tempo real (MATAR; PARADIS & IRAVANI, 2016).

A fim de compreender as interações e mitigar possíveis problemas é desejável que qualquer produto ou dispositivo seja anteriormente testado sob as condições mais pró-

ximas possível dos sistemas aos quais serão empregados. Neste contexto, a simulação PHIL pode prover uma alternativa de custo reduzido em relação ao custo de implantação do sistema real.

Outra motivação para esta abordagem reside na flexibilidade e facilidade para modificar as condições do sistema circundante, que é a parte simulada em tempo real, uma vez que as montagens experimentais de alta potência, totalmente implementadas em hardware, podem ser muito demoradas e custosas. Ademais, a simulação PHIL também oferece um cenário ideal para a coleta de dados experimentais do HUT, que podem ser utilizados na construção e validação de modelos de simulação do própio HUT, e assim melhorar e motivar os estudos para análises offline.

### 1.2 IDENTIFICAÇÃO DO PROBLEMA

Dentre as fontes renováveis de energia conectadas à rede, a solar fotovoltaica (PV) é a que mais cresceu nas últimas décadas, apresentando um crescimento exponencial em suas instalações. Em 2015 a capacidade mundial de potência instalada aumentou em 50 GW (CENTURY, 2016). Além disso, a implantação generalizada dos painéis solares é justificado por fatores como o aumento da eficiência da célula fotovoltaica (do inglês, Photovoltaic cell) (PV) a níveis de 34,5% (WALES, 2016) e a aprovação de políticas de incentivos por governos de diversos países (COMMISION, 2012).

Neste novo cenário, o uso extensivo de painéis solares conectados à rede elétrica de distribuição podem resultar em impactos indesejáveis na qualidade de energia, tais como: flutuação de tensão; injeção de harmônicos característicos e não-característicos; aumento dos níveis de tensão; desequilíbrios de tensão; sobrecarga em dispositivos controladores de tensão tais como transformadores de derivação de carga e reguladores de tensão de linha; aumento das perdas devido a um possível fluxo de potência inverso; ilhamentos não intencionais; operação indevida de equipamentos de proteção; e etc (KANDIL et al., 2015). Por outro lado, a filosofia da operação e controle dos sistemas de geração fotovoltaicos conectados à rede elétrica mudou nos últimos anos. Anteriormente, os sistemas PV funcionavam similarmente à uma fonte de corrente, apenas injetando a potência ativa oriunda da conversão no SEP (IEEE, 2000). Quando qualquer tipo de anormalidade era identificada no SEP, o sistema PV se desconectava automaticamente, retornando sua operação alguns minutos após a normalização do sistema. Essa estratégia funciona de maneira adequada quando a penetração de sistemas PV no SEP é desprezível, ou nos casos em que o sistema é conectado a um ponto forte da

rede, ou seja, a potência da instalação é muito menor que a potência de curto-circuito da barra.

Atualmente, o cenário descrito anteriormente não retrata mais a realidade, principalmente em países com grandes incentivos como a Alemanha (TROESTER, 2009). Com o intuito de se adequar a essa nova realidade, os códigos de rede e recomendações para o controle e operação de sistemas PV conectados à rede mudaram drasticamente (YANG; YANG & MA, 2014) (ALMEIDA et al., 2016). Ao invés do conversor cessar sua operação ao primeiro sinal de distúrbio, o sistema PV agora é obrigado a se manter conectado dando suporte ao SEP. Alguns destes requisitos para sistemas PV conectados à rede são:

- Permanecer conectado durante uma falta;

- Dar suporte à restauração da tensão fornecendo potência reativa durante a falta;

- Consumir a mesma potência reativa, ou menor, após a eliminação da falta;

- Alimentar a corrente de curto-circuito;

- A planta deve ser capaz de reduzir a potência ativa injetada para ajudar na regulação da frequência.

- Potência reativa deve ser injetada na rede de acordo com os requisitos do operador local durante a operação normal;

A fim de verificar com mais exatidão os impactos causados pela integração de sistemas PV à rede elétrica de distribuição, assim como estudar o comportamento e projetar sistemas de controle para operação do sistema PV durante condições anormais e curtos-circuitos, é necessário um ambiente em que todas essas possibilidades possam ser testadas. Neste contexto, a tecnologia PHIL pode ser uma alternativa interessante.

A UFJF conta com um sistema experimental de geração fotovoltaico de 30 kWp, dos quais metade são injetados na rede local através de conversores comerciais. Por ser diretamente conectado à rede interna da universidade, esse sistema não controlado não permite que parâmetros da rede sejam modificados e que situações de faltas sejam emuladas com segurança. Por outro lado, a UFJF também conta com um RTDS, equipamento consolidado para simulações em tempo real de SEPs. Entretanto, o RTDS não é indicado para simular conversores estáticos comutados a dezenas de kHz. Desta forma, a ideia principal deste projeto é unir o sistema experimental fotovoltaico ao

RTDS formando um PHIL que possibilitará todos os estudos de integração de sistemas PV ao SEP.

### 1.3 MOTIVAÇÃO DO TRABALHO

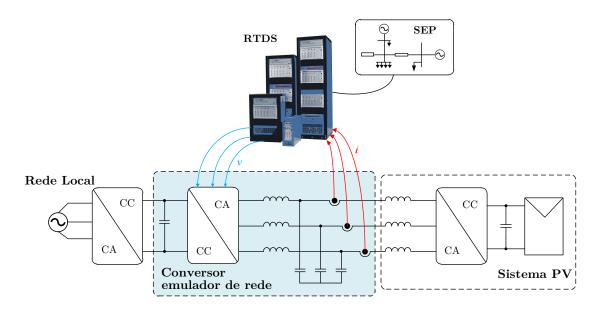

A Figura 2 ilustra uma estrutura PHIL conectada a um sistema PV, o qual deseja-se implementar na Universidade Federal de Juiz de fora (UFJF).

Figura 2: Estrutura PHIL conectado a um sistema PV.

O PHIL proposto na Figura 2 é composto por três estágios de conversão de energia. O sistema PV, que é o hardware sob teste desta topologia, utiliza um conversor CC-CA para injetar a energia convertida pelos painéis solares nos terminais do conversor emulador de rede (CER). Esta energia, que passa através do CER, será injetada por um outro conversor na rede elétrica local. Apesar de utilizar o PHIL, toda a energia gerada será disponibilizada para consumo na UFJF, da mesma forma que seria feito no caso da conexão direta.

O CER é a parte mais importante deste sistema. Ele é responsável por gerar as tensões nos terminais do sistema PV, de acordo com os sinais fornecidos pelo RTDS, independente da potência e da forma de onda de corrente injetada pelo sistema PV. O RTDS simula em tempo real o SEP, utilizando como entrada as correntes reais injetadas pelo sistema PV e fornece as tensões da barra em que o sistema PV está conectado. Desta forma, é possível, baseado em medições reais *online*, verificar a interação dos impactos do sistema PV no SEP, além de ser possível verificar experimentalmente a operação do sistema PV frente a condições anormais do SEP simulada pelo RTDS.

Com o auxílio do RTDS, propõe-se ao conversor emulador de rede, em destaque na Figura 2, fazer-se de rede elétrica local a fim de testar e estudar, em tempo real, os impactos que esta conexão proporciona ao sistema PV e ao sistema elétrico de potência (SEP), juntamente com o desempenho do sistema de controle da geração PV frente a condições anormais no SEP. Nesse sentido, o desenvolvimento de uma estratégia de controle eficiente é fundamental para garantir a operação satisfatória do PHIL.

Usualmente, há uma procura por controladores de fácil implementação e que apresentem desempenho dinâmico rápido e erros de regime permanentes nulos. Em grande parte das aplicações, esses controladores são projetados com uma malha interna de corrente para garantir uma maior robustez ao sistema de controle (KAZMIERKOWSKI & MALESANI, 1998). Contudo, este tipo de abordagem demanda a utilização de sensores de grande precisão adicionais, aumentando os custos.

Dos diversos controladores empregados na literatura pode-se citar as versões lineares, proporcional-integrador (PI) (MODESTO et al., 2013), proporcional-ressonante (PR) (LOH et al., 2003) deadbeat (DB) (MATTAVELLI, 2005) e não-lineares, controle por modos deslizantes (do inglês, sliding mode control) (SMC) (KOMURCUGIL, 2012) e preditivo (CORTES et al., 2009). Outra vertente que apresenta bons resultados, envolve as combinações de dois ou mais controladores com objetivo de conciliar boas características de cada estratégia de controle (LOH et al., 2003).

#### 1.4 OBJETIVOS

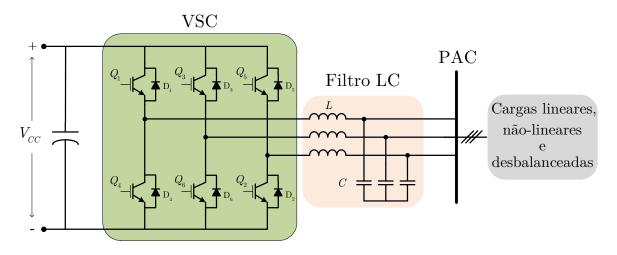

Devido à complexidade do sistema mostrado na Figura 2, esta dissertação terá como foco o conversor emulador de rede, um dos itens de fundamental importância do PHIL em questão.

O objetivo deste trabalho é desenvolver uma estratégia de controle para conversores estáticos fonte de tensão utilizados para formar uma rede elétrica trifásica de distribuição. Nesse contexto, o algoritmo de controle tem que ser capaz de gerar uma tensão trifásica fiel aos sinais de referência, independente das correntes drenadas ou injetadas nos terminais do CER.

Devido ao fato de que apenas o CER será implementado, não será possível testar o sistema da forma mostrada na Figura 2. Portanto, para testar a eficácia do controlador, o conversor emulador de rede será conectado à cargas lineares, não-lineares e desbalanceadas, como ilustrado na Figura 3. Apesar do fluxo de potência ser no

sentido contrário, o projeto do controlador é feito da mesma forma, uma vez que as correntes serão modeladas como distúrbio. Assim, o projeto de controle desenvolvido neste trabalho poderá ser utilizado sem adaptações quando o sistema de geração PV for incorporado. É importante, no entanto, utilizar uma estratégia *back-to-back* como ilustrado na Figura 2 tornando o sistema bidirecional em potência.

Figura 3: Conversor emulador de rede.

Assim, para atingir o principal objetivo deste trabalho as seguintes etapas foram planejadas e executadas:

- i. Modelar matematicamente o sistema sob estudo;

- ii. Estudar técnicas de controle de tensão para serem aplicadas a conversores fonte de tensão;

- iii. Simular o sistema modelado no software PSIM;

- iv. Apresentar uma técnica de controle alternativa para controlar o conversor VSC a fim de garantir uma tensão no PAC de alta qualidade mesmo quando alimentando cargas não-lineares;

- v. Implementar um protótipo em laboratório;

- vi. Implementar os algoritmos de controle desenvolvidos em um controlador digital de sinais (do inglês, *Digital Signal Controller*) (DSC) (TMS320F28335) da Texas Instruments;

- vii. Obter resultados experimentais para validar o modelo matemático e a estratégia de controle proposta.

#### 1.5 ESTRUTURA DO TRABALHO

Este trabalho é organizado em seis capítulos.

No Capítulo 2 é apresentada uma revisão das estratégias de controle aplicadas a conversores VSC com filtro LC. Em seguida, é apresentado um panorama da ressonância intrínseca do filtro de segunda ordem e, por fim, são discutidos os principais caminhos para atenuá-la.

No Capítulo 3 são apresentados o princípio de funcionamento do VSC e a modelagem do conversor fonte de tensão com filtro LC. Posteriormente é obtida a matriz de transferência que rege o comportamento do sistema para em seguida realizar a discretização do mesmo.

O Capítulo 4 aborda detalhes do projeto do controlador.

No Capítulo 5 são apresentados detalhes sobre a construção do protótipo, da implementação prática e da programação do processador digital de sinais (do inglês, Digital Signal Processor) (DSP). Resultados obtidos serão apresentados, discutidos e analisados.

O Capítulo 6 apresenta conclusões gerais deste trabalho, a produção científica resultante desta pesquisa e algumas propostas para a continuidade desta pesquisa serão feitas.

No Apêndice A são apresentados os diagramas esquemáticos dos circuitos de condicionamento e de interface dos sinais de corrente e tensão utilizados na implementação experimental do protótipo desenvolvido.

# 2 REVISÃO DE CONTROLADORES DE TENSÃO PARA CONVERSORES ESTÁTICOS COM FILTROS LC

# 2.1 INTRODUÇÃO

Existem duas estratégias básicas para controlar conversores fonte de tensão. Uma delas é denominada controle modo de corrente (do inglês, current-mode control) (CMC). Nesta estratégia, um controlador de corrente na malha interna dedicado proporciona uma regulação de corrente eficiente, reduzindo picos e protegendo todo o sistema contra sobrecorrente.

A oura estratégia é conhecida como controle modo de tensão (do inglês, voltage-mode control) (VMC) e é amplamente utilizado em aplicações de alta potência. Nesta estratégia, usualmente não existe malha interna de corrente, sendo a tensão nos terminais do conversor controlada por malha única de tensão. Apesar de simples e empregar poucas malhas de controle, deve-se prever uma malha interna para proteger o conversor contra sobrecorrentes ou correntes de curto-circuito (YAZDANI & IRAVANI, 2010).

Neste capítulo serão investigados alguma estratégias utilizadas na literatura para controlar e garantir que as tensões no PAC rastreiem os sinais de referência e ao mesmo tempo rejeite possíveis distúrbios causados por cargas conectadas no PAC.

### 2.2 ESTRATÉGIAS DE CONTROLE APLICADAS A CONVERSO-RES VSC COM FILTRO LC

Na Figura 4 é ilustrada a estrutura básica de um conversor fonte de tensão de dois níveis, a três fios e com filtro de saída LC alimentando cargas conectadas no PAC. O filtro LC, devido ao capacitor em paralelo com a carga, é utilizado quando se deseja emular o comportamento de uma rede elétrica, ou seja, controlar as tensões no ponto de acoplamento comum onde as cargas são conectadas. Este filtro, embora possa comprometer a estabilidade do sistema devido à ressonância intrínseca, atenua melhor os harmônicos de comutação se comparado ao filtro indutivo de primeira ordem.

Figura 4: Estrutura básica de um VSC com filtro de saída LC alimentando cargas locais

Como estes conversores operam de forma isolada, eles tem a finalidade de emular as tensões de uma rede elétrica de distribuição. Nesse contexto, as estratégias de controle utilizadas em sistemas fonte ininterrupta de energia (do inglês, *Uninterruptible Power Supply*) (UPS), microrredes isoladas e entre outras, se aplicam a este trabalho. Sendo, portanto, importante a revisão das estratégias propostas na literatura.

O principal papel de uma UPS é manter a tensão e a frequência de alimentação dentro de faixas preestabelecidas por normas específicas, sob quaisquer condições de carga. Para alcançar este resultado, diferentes algoritmos de controle tem sido propostos na literatura, que vão desde controladores lineares como proporcional-integral,  $H_{\infty}$ , deadbeat, repetitivo, até controladores não-lineares como modos deslizantes e controle por linearização da realimentação (do inglês, Feedback Linearization Control) (FLC) e etc..

O controle PI sugerido em (KARIMI; YAZDANI & IRAVANI, 2011) e (MODESTO et al., 2013) é de fácil implementação, porém a tensão de saída apresenta uma alta distorção harmônica total (do inglês,  $Total\ Harmonic\ Distortion$ ) (THD) quando cargas não-lineares são alimentadas. Em (LEE; CHIANG & CHANG, 2001) o controle  $H_{\infty}$  é descrito e implementado em um inversor monofásico adicionando robustez ao sistema. Um controlador preditivo, aplicado ao sistema UPS, é descrito em (CORTES et al., 2009). Nele, os autores substituem os sensores de corrente na carga por observadores de corrente para reduzir o custo do sistema. No entanto, a simulação e os resultados experimentais não revelaram melhoras significativas em termos de THD e erro em estado estacionário. O controlador proposto por (MATTAVELLI, 2005) utiliza o controle deadbeat aliado a observadores de estado e de distúrbio com o objetivo de suprimir ou diminuir incertezas causadas por variações paramétricas da planta e aos ruídos de medição. Em (KUKRER; KOMURCUGIL & DOGANALP, 2009) e (KOMURCUGIL, 2012)

a aplicação da técnica de controle por modos deslizantes garante robustez frente a distúrbios e variações paramétricas, embora esta estratégia esteja associada com o fenômeno indesejável de *chattering* (TAN; LAI & TSE, 2011). Tal fenômeno é inerente aos conversores estáticos e está relacionado à variação entre as subestruturas do dispositivo que, por sua vez, ocorrem em uma frequência finita (SILVA & PINTO, 2011). É indesejado na medida em que leva a uma menor precisão no controle dos conversores, desgaste de partes mecânicas em servomotores e em outros elementos, bem como o aumento de perdas por comutação (UTKIN; GULDNER & SHI, 2009). Em (ESCOBAR et al., 2007) e (BOTTERÓN & PINHEIRO, 2007), o controle repetitivo é aplicado para alcançar uma tensão de saída com baixo THD. No entanto, geralmente, esta técnica de controle apresenta uma resposta transitória lenta (KIM et al., 2015). Um controle adaptativo com baixa THD é proposto em (DO et al., 2013). Já o controle de linearização por realimentação é proposto em (KIM & LEE, 2010).

Além das estratégias de controle abordadas acima, outros trabalhos tem destacado o uso dos controladores proporcional-integral e derivativo (PID) com malhas em cascata devido à sua facilidade de implementação e desempenho satisfatório (LOH et al., 2003).

Os controladores de conversores estáticos podem ser projetados com uma, duas ou mais malhas de controle. Na estratégia com duas malhas, geralmente é incluída uma malha interna de corrente e uma malha externa de tensão. A primeira garante proteção contra sobrecorrente e proporciona robustez contra variações nos parâmetros do sistema, enquanto a segunda promove o valor de referência para o controlador de corrente além do controle de tensão.

O controle de corrente, em esquemas de mais uma malha, pode adotar a corrente no capacitor ou a corrente no indutor como principal variável da realimentação interna. Nesse contexto, devido ao fato de ser a estratégia mais utilizada, esta seção apresenta uma revisão detalhada, proposta em (LOH et al., 2003), dos méritos e das deficiências destas alternativas.

A fim de reduzir o erro de estado permanente, compensadores PR podem ser incluídos na malha externa de tensão. O PR ideal introduz um ganho infinito na frequência de ressonância selecionada de maneira a eliminar o erro de regime permanente nesta frequência. Dentre as suas diversas características, destaca-se a dispensabilidade de estimar precisamente os parâmetros do sistema ao qual o PR está inserido. Em (ALMEIDA, 2013) é realizada uma revisão mais detalhada deste controlador.

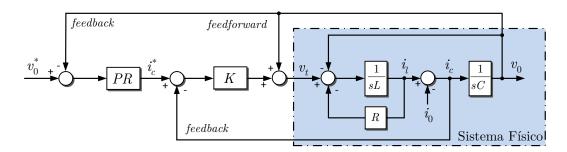

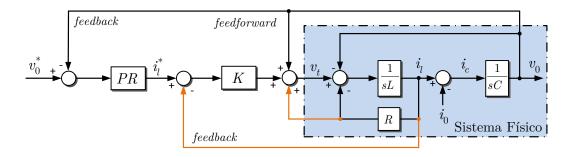

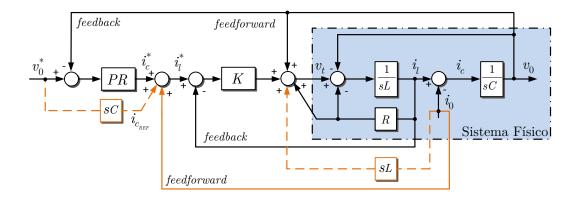

Nas Figuras 5, 6 e 7 são ilustradas as principais estruturas de controle multi-malha

aplicadas aos sistemas UPS. Note que as estruturas das Figuras 5 e 6 utilizam a corrente no capacitor  $(i_c)$  e no indutor  $(i_l)$ , respectivamente, como variável de realimentação interna. Além disso, em ambas alternativas há uma compensação feed-forward da tensão de saída  $(v_0)$ , além da compensação feed-forward da corrente no indutor no esquema da Figura 6.

A estrutura da Figura 7 é considerada mais complexa, uma vez que ela propõe utilizar as correntes no indutor e na carga  $(i_0)$  como variáveis de realimentação e de feed-forward. Por este motivo, este esquema exige sensores de corrente adicionais, que podem impactar o custo da UPS.

Figura 5: Controle da tensão de saída utilizando a corrente no capacitor na realimentação interna.

Figura 6: Controle da tensão de saída utilizando a corrente no indutor na realimentação interna.

Se, na Figura 7, o controlador PR fosse substituído pelo controlador PI, seria necessário incluir o bloco sC na malha externa de tensão, a fim de compensar o erro de rastreamento da tensão de referência. Este bloco estima a corrente no capacitor e com isso reduz o erro de estado permanente senoidal da tensão de saída (MODESTO et al., 2013).

A equação que descreve a dinâmica do sistema com a inclusão do controle proposto na Figura 5 é dada por:

Figura 7: Controle da tensão de saída utilizando a corrente no indutor e corrente na carga.

$$v_{0}(s) = \underbrace{\frac{KG_{R}(s)}{s^{2}LC + (RC + CK)s + KG_{R}(s)}}_{\text{Primeiro termo}} v_{0}^{*}(s) - \underbrace{\frac{sL + R}{s^{2}LC + (RC + CK)s + KG_{R}(s)}}_{\text{Segundo termo } Z_{0c}(s)} i_{0}(s), \qquad (2.1)$$

Os primeiro e segundo termos de (2.1) relacionam a tensão de saída com a tensão de referência e a corrente na carga, respectivamente. O ganho K é um controlador proporcional usualmente utilizado na malha interna de corrente e  $G_R(s)$  é a função de transferência do controlador proporcional ressonante, geralmente incluído na malha externa de tensão. Controladores de ordem mais alta também podem ser utilizados, entretanto, além do controlador proporcional ser largamente aplicado, ele facilita uma análise preliminar.

Baseado em (2.1), pode-se afirmar que o segundo termo desta equação é denominado impedância de saída do sistema  $(Z_{0c}(s))$ , e que a sua inversa, nomeada como rigidez dinâmica, quantifica a capacidade da corrente consumida pela carga produzir uma queda unitária na tensão de saída. Isto posto, a corrente na carga pode ser considerada uma perturbação para o sistema (LOH et al., 2003).

Como dito anteriormente, o controlador PR apresenta um ganho infinito na frequência de ressonância selecionada, ou seja,  $G_R(j\omega_r) \to \infty$ . Desta forma, em (2.1), a tensão de saída se aproxima da tensão de referência  $(v_0^*)$  na frequência de ressonância do PR, sem a necessidade de estimar os parâmetros do sistema UPS.

Por outro lado, quando a corrente no indutor é utilizada como variável de reali-

mentação interna (Figura 6), a seguinte relação entre a variável de saída, a referência e o distúrbio pode ser escrita

$$v_{0}(s) = \underbrace{\frac{KG_{R}(s)}{s^{2}LC + (RC + CK)s + KG_{R}(s)}}_{\text{Primeiro termo}} v_{0}^{*}(s) - \underbrace{\frac{sL + K + R}{s^{2}LC + (RC + CK)s + K(s)G_{R}(s)}}_{\text{Segundo termo } Z_{0i}(s)} i_{0}(s), \qquad (2.2)$$

Novamente, sob condições de estado permanente, o ganho infinto introduzido pelo controlador PR faz com que a tensão de saída rastreie a tensão de referência, ou seja,

$$\lim_{s \to j\omega_r} \frac{v_0(s)}{v_0^*(s)} \to 1, \tag{2.3}$$

e que rejeite as perturbações causadas pela correntes na carga,

$$\lim_{s \to j\omega_r} \frac{v_0(s)}{i_0(s)} \to 0. \tag{2.4}$$

É importante ressaltar que as afirmações anteriores são validas apenas para a frequência  $\omega_r$  em que o controlador ressonante foi projetado.

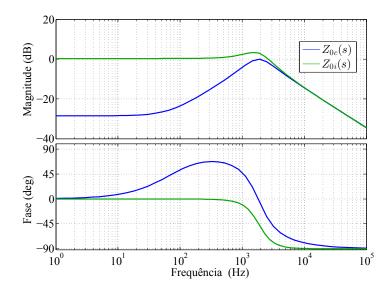

Embora as estratégias de controle propostas nas Figuras 5 e 6 sejam plenamente conhecidas na literatura, elas são deficientes frente a distúrbios harmônicos causados pela carga. Uma das alternativas para eliminar estas perturbações é reduzir o filtro indutivo, reduzindo assim a impedância de saída. Contudo, apenas esta estrategia não é satisfatória para o controle que utiliza a corrente no indutor como única variável de realimentação, uma vez que a impedância de saída do sistema  $(Z_{0i}(s))$ , segundo termo da equação (2.2), contém o ganho K no numerador. Portanto, a redução dos distúrbios causados pela carga depende da redução da impedância do filtro e também do valor do ganho proporcional K. Outra alternativa interessante para ambos casos é utilizar compensadores PRs individuais sintonizados nas frequências de cada componente que se deseja rejeitar.

Note que os pólos da impedância de saída para os controles de corrente no capacitor e indutor são os mesmos, no entanto o zero é diferente. O ganho K aumenta a frequência do zero em  $Z_{0i}(s)$ , e com isso, faz com que este sistema seja mais sensível a distúrbios

em baixa frequência. Na Figura 8 é ilustrado este comportamento. Para esta análise, considerou-se o controlador ressonante com ganho unitário e K=2.

Figura 8: Diagrama de bode das impedâncias de saída para dois tipos de controladores, considerando  $G_R(s) = 1$ .

Segundo (LOH et al., 2003), o diagrama de blocos da Figura 5, que realimenta a corrente no capacitor, obteve melhor desempenho. Entretanto, em sistemas que não medem as correntes de saída do VSC não é possível realizar proteção contra sobrecorrente.

No diagrama de blocos da Figura 6 é realizada a medição das correntes que saem do inversor. Isto viabiliza incluir facilmente a proteção contra sobrecorrente no algoritmo de controle. Neste mesmo contexto, pode-se destacar que a proposta da Figura 7 é a mais custosa das três. Ela necessita de dois sensores de corrente, de alto desempenho, por fase para medir as correntes da carga e no indutor. Contudo, este controlador reúne o mesmo desempenho do controle de corrente no capacitor, com a vantagem de proteger o inversor contra sobrecorrentes (LOH et al., 2003).

### 2.3 RESSONÂNCIA DOS FILTROS LC

Os harmônicos de comutação oriundos dos conversores eletrônicos de potência são atenuados através de filtros passivos, a partir de filtros mais simples, L, até filtros de ordem superior, LC, LCL e etc. No entanto, em sistemas com filtros de segunda ordem ou superior, a presença destes componentes armazenadores de energia geram ressonância (BAI et al., 2016). Tais ressonâncias podem ser atenuadas por adição de amortecedores passivos ou ativos. Os amortecedores passivos utilizam resistores fí-

sicos, que adicionam perdas de energia e são sensíveis às variações paramétricas do sistema (BERES et al., 2016). Os amortecedores ativos são comumente utilizados na literatura. Eles conseguem atenuar a ressonância dos filtros LC através das estratégias de controle do conversor estático (LI, 2009).

O amortecimento harmônico através da resistência virtual e as técnicas de control-signal-shaping são algumas alternativas capazes de reduzir a ressonância em um conversor estático com filtro LC. O primeiro método cria uma resistência fictícia, similar

à resistência física, e a utiliza somente nas frequências harmônicas. No entanto, o

processo de filtragem neste método pode apresentar uma resposta dinâmica ruim (LI,

2009).

O método control-signal-shaping molda o sinal da modulação por largura de pulso (do inglês, Pulse Width Modulation) (PWM), mediante a uma sequência de degraus, para cancelar o efeito oscilatório da ressonância (ZHONG & HANG, 2004). Esta alternativa é mais indicada para sistemas de conversão com frequência de ressonância fixa.

#### 2.3.1 AMORTECIMENTO PASSIVO

O amortecimento passivo geralmente utiliza resistência série e/ou paralelo para amortecer a ressonância, o que pode comprometer a eficiência do sistema. Como maneira de superar este problema, elementos passivos adicionais, tais como L, C ou a combinação deles, podem ser usados. No entanto, isto aumenta a complexidade do sistema.

Na conexão em série, quanto maior o valor da resistência melhor o amortecimento da ressonância, contudo, mais pobre será atenuação de harmônicos em altas frequências (BüYüK et al., 2016).

Na topologia em paralelo, adicionar o resistor em paralelo com o capacitor é a melhor opção pois ele oferece mais estabilidade ao sistema (BüYüK et al., 2016).

#### 2.3.2 AMORTECIMENTO ATIVO

Na Figura 9 é ilustrado o diagrama de blocos para controlar a tensão em um sistema VSC utilizando apenas uma única malha de realimentação. Tal controle é geralmente usado para reduzir gastos com sensores de corrente e ainda manter uma boa capacidade de rastrear a referência de tensão. Contudo, esta estratégia é sensível frente a distúrbios em frequências vizinhas à frequência de ressonância. A fim de garantir maior robustez

ao sistema, uma malha interna de corrente pode ser inserida ao controlador da Figura 9.

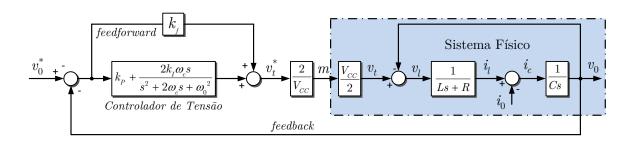

Figura 9: Estratégia de controle de um VSC utilizando uma malha de controle.

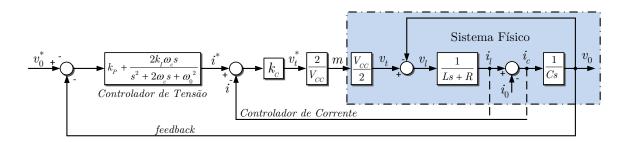

Como dito na seção anterior, controladores com duas malhas de controle podem utilizar tanto corrente no indutor quanto a corrente no capacitor como variável de realimentação, conforme ilustrado na Figura 10.

Figura 10: Estratégia de controle de um VSC utilizando duas malhas de controle.

Enquanto controlar a corrente no capacitor é a melhor alternativa para rejeitar distúrbios causados pela carga, controlar a corrente no indutor é a melhor opção para amortecer a ressonância gerada pelo filtro *LC* (LI, 2009).

A função de transferência da malha interna de corrente é,

$$G_{V(in)} = \frac{k_C}{s^2 LC + (CR + Ck_C)s + 1}$$

(2.5)

onde  $k_C$  é o ganho do controlador de corrente.

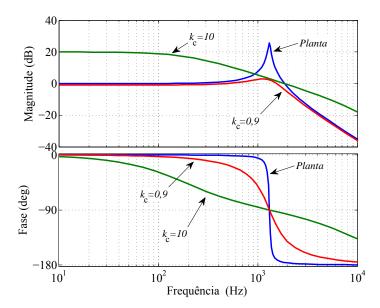

Com base em (2.5) fica claro a influência do ganho  $k_C$  no amortecimento dos polos da função de transferência. Para ilustrar esta característica, a Figura 11 destaca as respostas em frequência da malha interna de corrente para diferentes valores de  $k_C$ . Observe que o pico de ressonância diminui conforme o ganho  $k_C$  aumenta. No entanto, maior valores de ganho  $k_C$  introduzem um maiores atraso de fase na frequência de operação do sistema.

Figura 11: Respostas em frequência do controlador de corrente para diferentes ganhos.

### 2.4 CONCLUSÕES PARCIAIS

Neste capítulo foi apresentado uma revisão sucinta de algumas maneiras de controlar as tensões em um VSC na configuração emulador de rede elétrica. Em seguida foram detalhadas as topologias mais usuais de controle apresentadas na literatura técnica. Foi visto que as estratégias que utilizam duas malhas de controle garantem robustez ao sistema e também proteção contra sobrecorrente. Além disso, o controle com a realimentação da corrente no capacitor é citada na literatura como a que possui melhor desempenho dinâmico. Todavia, para garantir proteção contra sobrecorrente, é preciso medir as correntes de saída do VSC.

O problema da ressonância, gerada pela interação entre os componente reativos do filtro de saída, também foi abordado. Para atenuar este fenômeno, os amortecedores ativos, que usam duas malhas de controle, são mais indicados. Entretanto, seus ganhos têm de ser criteriosamente calculados para não comprometer a filtragem de componentes harmônicos de alta frequência.

## 3 FUNDAMENTOS TEÓRICOS

# 3.1 INTRODUÇÃO

Neste capítulo são apresentados os conceitos básicos envolvendo o funcionamento do conversor emulador de rede elétrica. Além disso, são apresentada, de maneira sucinta, algumas características sobre o princípio de funcionamento dos conversores fonte de tensão trifásico, assim como a modelagem matemática do CER.

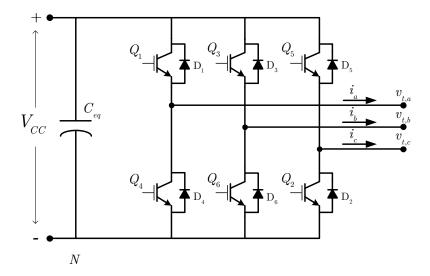

### 3.2 FUNCIONAMENTO BÁSICO DO CONVERSOR FONTE DE TEN-SÃO TRIFÁSICO

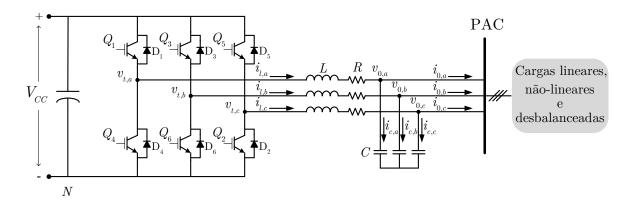

Na Figura 12 é mostrada a topologia básica de um VSC trifásico composto por seis interruptores semicondutores do tipo Transistor Bipolar com Gatilho Isolado (do inglês, Insulated Gate Bipolar Transistor) (IGBT) e com seis diodos conectados em antiparalelo. Geralmente, o capacitor CC ( $C_{eq}$ ) é grande o suficiente para garantir uma tensão CC com ondulação desprezível nos terminas de entrada do conversor. Interruptores de um mesmo braço são acionados de maneira complementar de modo a evitar um possível curto-circuito no capacitor CC.

Em vista disso, para cada terminal CA do VSC, pode-se formular a seguinte relação para a tensão de saída, em relação ao terminal negativo N,

$$v_{t,x} = \begin{cases} +V_{CC}, & \text{quando o interruptor superior est\'a ativo} \\ 0, & \text{quando o interruptor inferior est\'a ativo} \end{cases}$$

(3.1)

onde  $V_{CC}$  é o valor da tensão no barramento CC e  $x \in \{a,b,c\}$ .

Na literatura há diferentes estratégias para determinar o padrão de comutação com o objetivo de controlar a magnitude e fase das tensões e correntes geradas nos terminais CA dos conversores VSC. Maiores informações sobre as técnicas de modulação por

Figura 12: Diagrama de um conversor fonte de tensão trifásico.

largura de pulso (PWM) podem ser encontradas em (HOLMES & LIPO, 2003), (MOHAN; UNDELAND & ROBBINS, 2003), (SKVARENINA, 2002) e (KAŹMIERKOWSKI; KRISHNAN & BLAABJERG, 2002).

#### 3.3 O VETOR ESPACIAL

De acordo com (YAZDANI & IRAVANI, 2010), o vetor ou fasor espacial é uma generalização do fasor convencional onde é possível representar grandezas trifásicas. Esta variável única carrega informações da amplitude, do ângulo de fase e da frequência da grandeza trifásica instantânea.

Considerando as componentes instantâneas, em um instante de tempo t, de um sistema de tensões trifásicas equilibradas, conforme ilustrado na Figura 13, pode-se encontrar o fasor espacial através da seguinte relação

$$\vec{v}(t) = \frac{2}{3} \left[ e^{j0} v_a(t) + e^{j\frac{2\pi}{3}} v_b(t) + e^{j\frac{4\pi}{3}} v_c(t) \right] , \qquad (3.2)$$

cuja representação geométrica está representada na Figura 14.

A constante 2/3 foi incluída em (3.2) para garantir invariância em amplitude, ou seja, os vetores espaciais terão a mesma amplitude das grandezas elétricas de fase.

De acordo com a descrição matemática apresentada previamente, as tensões e correntes trifásicas podem ser representadas pela projeção do fasor espacial em um sistema estático de coordenadas ortogonais denominado  $\alpha\beta$ , ou seja,

Figura 13: Componentes instantâneas: (a) fase a, (b) fase b, (c) fase c.

Figura 14: Representação do vetor espacial de tensão nos sistemas de coordenadas (abc).

$$\vec{v}(t) = v_{\alpha\beta} = v_{\alpha} + jv_{\beta}. \tag{3.3}$$

A Figura 15 ilustra a representação gráfica do fasor espacial  $\vec{v}$ , sem componente de sequência zero, referenciado nos sistemas de coordenadas (abc) e  $(\alpha\beta)$ .

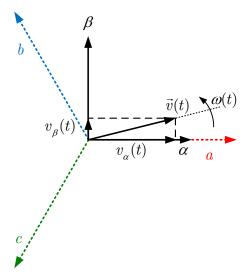

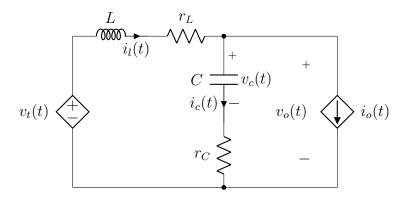

#### 3.4 MODELAGEM DO CONVERSOR EMULADOR DE REDE

Na modelagem matemática do conversor VSC é usado o conceito de fasor espacial, apresentado em (YAZDANI & IRAVANI, 2010). Desse modo, desprezando os harmônicos gerados pela comutação dos interruptores do VSC, pode-se representar a conexão do conversor emulador de rede com as cargas locais através do circuito equivalente da Figura 16, em que L, C,  $r_L$  e  $r_C$  são, respectivamente, o indutor, o capacitor e as resistências série equivalente dos respectivos elementos do filtro de saída. A tensão de saída do conversor  $v_t(t)$  é representada como um fonte de tensão controlada. Já a fonte de corrente  $i_o(t)$  representa a corrente consumida pela carga, considerada como um

Figura 15: Representação gráfica do vetor espacial de tensão nos sistemas de coordenadas  $(\alpha\beta0)$ .

distúrbio para o controle da tensão de saída  $v_o(t)$ .

Figura 16: Equivalente monofásico do CER.

Aplicando a lei das tensões de Kirchhoff no circuito monofásico equivalente mostrado na Figura 16, pode-se escrever as seguintes relações para cada uma das fases do VSC trifásico:

$$\begin{cases}

L \frac{di_{l,a}(t)}{dt} = v_{t,a}(t) - r_L i_{l,a}(t) - v_{o,a}(t) \\

L \frac{di_{l,b}(t)}{dt} = v_{t,b}(t) - r_L i_{l,b}(t) - v_{o,b}(t) , \\

L \frac{di_{l,c}(t)}{dt} = v_{t,c}(t) - r_L i_{l,c}(t) - v_{o,c}(t)

\end{cases}$$

(3.4)

onde  $v_{t,x}(t)$  é a tensão instantânea de fase nos terminais de saída do VSC;  $i_{l,x}(t)$  é a

corrente instantânea de fase nos terminas de saída do VSC;  $v_{o,x}(t)$  é a tensão no ponto de acoplamento comum (PAC), sendo que  $x \in \{a,b,c\}$ .

Por outro lado, aplicando a lei de Kirchhoff das correntes no terminal do capacitor encontra-se as seguintes equações

$$\begin{cases}

C \frac{dv_{c,a}(t)}{dt} = i_{l,a}(t) - i_{o,a}(t) \\

C \frac{dv_{c,b}(t)}{dt} = i_{l,b}(t) - i_{o,b}(t) , \\

C \frac{dv_{c,c}(t)}{dt} = i_{l,c}(t) - i_{o,c}(t)

\end{cases}$$

(3.5)

onde  $v_{c,x}(t)$  é a tensão instantânea de fase nos terminas do capacitor VSC;  $i_{c,x}(t)$  é a corrente instantânea de fase através do capacitor;  $i_{o,x}(t)$  é a corrente da carga, sendo que  $x \in \{a,b,c\}$ ;

Finalmente, a tensão na carga é dada por

$$\begin{cases} v_{o,a}(t) = v_{c,a}(t) + r_C i_{c,a}(t) \\ v_{o,b}(t) = v_{c,b}(t) + r_C i_{c,b}(t) , \\ v_{o,c}(t) = v_{c,c}(t) + r_C i_{c,c}(t) \end{cases}$$

(3.6)

Relacionando as variáveis instantâneas de (3.4), (3.5) e (3.6) com (3.2) pode-se representar o sistema de equações na forma compacta através de:

$$L\frac{d\vec{i}_{l}(t)}{dt} = \vec{v}_{t}(t) - r_{L}\vec{i}_{l}(t) - \vec{v}_{o}(t) , \qquad (3.7)$$

onde  $\vec{i}_l(t)$ ,  $\vec{v}_t(t)$  e  $\vec{v}_o(t)$  são vetores espaciais de corrente e tensão nos terminais do VSC e no PAC, respectivamente,

$$C\frac{d\vec{v}_c(t)}{dt} = \vec{i}_l(t) - \vec{i}_o(t) , \qquad (3.8)$$

onde  $\vec{v}_c(t)$ ,  $\vec{i}_c(t)$  e  $\vec{i}_o(t)$  são vetores espaciais de tensão e corrente nos terminais do capacitor e na carga, respectivamente, e

$$\vec{v}_o(t) = \vec{v}_c(t) + r_C \vec{i}_c(t) . {3.9}$$

O espaciais de (3.7), (3.8) e (3.9) podem também ser escritos em função das componentes  $\alpha$  e  $\beta$  como se segue

$$L\frac{d\vec{i}_{l,\alpha\beta}(t)}{dt} = \vec{v}_{t,\alpha\beta}(t) - r_L \vec{i}_{l,\alpha\beta}(t) - \vec{v}_{o,\alpha\beta}(t) , \qquad (3.10)$$

$$C\frac{d\vec{v}_{c,\alpha\beta}(t)}{dt} = \vec{i}_{l,\alpha\beta}(t) - \vec{i}_{o,\alpha\beta}(t) , e$$

(3.11)

$$\vec{v}_{\alpha,\alpha\beta}(t) = \vec{v}_{\alpha,\alpha\beta}(t) + r_C \vec{i}_{\alpha,\alpha\beta}(t) , \qquad (3.12)$$

onde  $\vec{v}_{t,\alpha\beta}(t)$ ,  $\vec{i}_{l,\alpha\beta}(t)$ ,  $\vec{v}_{c,\alpha\beta}(t)$ ,  $\vec{i}_{c,\alpha\beta}(t)$ ,  $\vec{v}_{o,\alpha\beta}(t)$ ,  $\vec{i}_{o,\alpha\beta}(t)$  são os respectivos vetores espaciais referenciados em um sistema de coordenadas ortogonais  $\alpha\beta$ .

## 3.5 REPRESENTAÇÃO NO ESPAÇO DE ESTADOS

Além de ser representados como equações diferenciais, os sistemas (3.10), (3.11) e (3.12) podem também ser representados na forma generalizada em espaço de estados (OGATA, 2010):

$$\begin{cases} \dot{\mathbf{x}} = \mathbf{A}\mathbf{x} + \mathbf{B}\mathbf{u} \\ \mathbf{y} = \mathbf{C}\mathbf{x} + \mathbf{D}\mathbf{u} \end{cases}$$

(3.13)

onde

$$\mathbf{A} = \begin{bmatrix} \mathbf{A}_{\alpha} & \mathbf{0}_{2} \\ \mathbf{0}_{2} & \mathbf{A}_{\beta} \end{bmatrix}, \mathbf{B} = \begin{bmatrix} \mathbf{B}_{\alpha} \\ \mathbf{B}_{\beta} \end{bmatrix}, \mathbf{C} = \begin{bmatrix} \mathbf{C}_{\alpha} & \mathbf{0}_{2} \\ \mathbf{0}_{2} & \mathbf{C}_{\beta} \end{bmatrix}, \mathbf{D} = \begin{bmatrix} \mathbf{D}_{\alpha} \\ \mathbf{D}_{\beta} \end{bmatrix}, \quad (3.14)$$

são as matrizes de transição de estado, entrada, saída e de transmissão direta, respectivamente;  $\mathbf{0}_2$  são matrizes quadradas de zeros, em que o subscrito representa sua dimensão;  $\mathbf{x} = \begin{bmatrix} \mathbf{x}_{\alpha}^T & \mathbf{x}_{\beta}^T \end{bmatrix}^T$  é o vetor de estados,  $\mathbf{u} = \begin{bmatrix} \mathbf{u}_{\alpha}^T & \mathbf{u}_{\beta}^T \end{bmatrix}^T$  é o vetor de entrada e  $\mathbf{y} = \begin{bmatrix} \mathbf{y}_{\alpha}^T & \mathbf{y}_{\beta}^T \end{bmatrix}^T$  é o vetor de saída; o sobrescrito ( $^T$ ) representa o operador de

transposição. As matrizes de (3.14) são dadas por

$$\mathbf{A}_{\alpha} = \mathbf{A}_{\beta} = \begin{bmatrix} \frac{-r_L + r_C}{L} & -\frac{1}{L} \\ \frac{1}{C} & 0 \end{bmatrix}, \tag{3.15}$$

$$\mathbf{B}_{\alpha} = \mathbf{B}_{\beta} = \begin{bmatrix} \frac{1}{L} & \frac{r_C}{L} \\ 0 & -\frac{1}{C} \end{bmatrix}, \tag{3.16}$$

$$\mathbf{C}_{\alpha} = \mathbf{C}_{\beta} = \begin{bmatrix} 1 & 0 \\ \\ r_C & 1 \end{bmatrix}, \tag{3.17}$$

$$\mathbf{D}_{\alpha} = \mathbf{D}_{\beta} = \begin{bmatrix} 0 & 0 \\ \\ 0 & -r_C \end{bmatrix}, \tag{3.18}$$

$$\mathbf{x}_{\alpha} = \begin{bmatrix} i_{l,\alpha}(t) & v_{c,\alpha}(t) \end{bmatrix}, \quad \mathbf{x}_{\beta} = \begin{bmatrix} i_{l,\beta}(t) & v_{c,\beta}(t) \end{bmatrix}, \tag{3.19}$$

$$\mathbf{u}_{\alpha} = \begin{bmatrix} v_{t,\alpha}(t) & i_{o,\alpha}(t) \end{bmatrix}, \quad \mathbf{u}_{\beta} = \begin{bmatrix} v_{t,\beta}(t) & i_{o,\beta}(t) \end{bmatrix}, \tag{3.20}$$

$$\mathbf{y}_{\alpha} = [i_{l,\alpha}(t) \quad v_{o,\alpha}(t)] \quad e \quad \mathbf{y}_{\beta} = [i_{l,\beta}(t) \quad v_{o,\beta}(t)].$$

(3.21)

Utilizando a transformada de *Laplace* com condições iniciais nulas, a matriz de transferência do sistema acima pode ser calculada por:

$$\mathbf{G}(s) = \mathbf{C}(s\mathbf{I} - \mathbf{A})^{-1}\mathbf{B} + \mathbf{D},\tag{3.22}$$

onde,

$$\mathbf{G}(s) = \begin{bmatrix} \mathbf{G}_{\alpha}(s) & \mathbf{0}_{2} \\ \mathbf{0}_{2} & \mathbf{G}_{\beta}(s) \end{bmatrix}. \tag{3.23}$$

Portanto, aplicando as matrizes dadas em (3.14) na relação (3.22), encontra-se as funções de transferência que regem o comportamento dinâmico do CER através de:

$$\mathbf{G}_{\alpha}(s) = \mathbf{G}_{\beta}(s) = \begin{bmatrix} Y_{in}(s) & T_{oi}(s) \\ G_{io}(s) & -Z_{o}(s) \end{bmatrix}, \tag{3.24}$$

onde  $Y_{in}(s)$  é a admitância de entrada;  $T_{oi}(s)$  é a função de transferência da entrada pela saída;  $G_{io}(s)$  é a função de transferência da saída pela entrada; e  $Z_o(s)$  é a impedância de saída do sistema.

Sabendo que a matriz de transferências relaciona as componentes  $\alpha\beta$  de saída pelas de entrada, ou seja,

$$\mathbf{Y}(s) = \mathbf{G}(s)\mathbf{U}(s),\tag{3.25}$$

onde  $\mathbf{U} = [v_{t,\alpha}(s) \ i_{o,\alpha}(s) \ v_{t,\beta}(s) \ i_{o,\beta}(s)]^T$  e  $\mathbf{Y} = [i_{l,\alpha}(s) \ v_{o,\alpha}(s) \ i_{l,\beta}(s) \ v_{o,\beta}(s)]^T$ , a dinâmica da tensão de saída no domínio da frequência pode ser representada como:

$$\begin{cases} v_{o,\alpha}(s) = G_{io}(s)v_{t,\alpha}(s) - Z_{o}i_{o,\alpha}(s) \\ v_{o,\beta}(s) = G_{io}(s)v_{t,\beta}(s) - Z_{o}i_{o,\beta}(s) \end{cases}$$

(3.26)

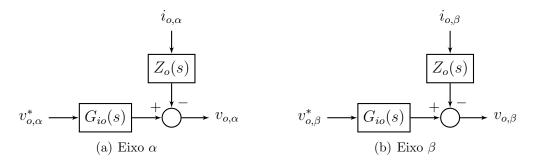

O sistema de equações (3.26) pode ser representado na forma do diagrama de blocos mostrado na Figura 17, usualmente utilizado na análise e projeto de controladores.

Figura 17: Representação em diagrama de blocos do sistema.

A impedância de saída do conversor e a função de transferência entrada/saída são dadas respectivamente por

$$Z_o(s) = \frac{L C r_C s^2 + (C r_C r_L + L)s + r_L}{L C s^2 + (r_C + r_L)C s + 1},$$

(3.27)

е

$$G_{io}(s) = \frac{C r_C s + 1}{L C s^2 + (r_C + r_L)C s + 1}.$$

(3.28)

Como já mencionado anteriormente, a impedância de saída  $(Z_o)$  é um parâmetro que influencia altamente o desempenho do sistema. A Figura 17 mostra claramente sua influência no controle da tensão  $v_o$ . A inversa de  $Z_o$  é denominada rigidez dinâmica, sendo definida como a amplitude de corrente drenada pela carga capaz de produzir um desvio unitário na tensão de saída (LOH et al., 2003). Já do ponto de vista de controle, esta corrente é tratada como um distúrbio que pode ser rejeitado se o ganho da impedância de saída for baixo o suficiente nas componentes de frequências da corrente drenada pela carga  $i_o$ .

Analisando a Figura 17 fica evidente que comportamento das variáveis nas coordenadas  $\alpha$  e  $\beta$  é desacoplado, ou seja, variações em um eixo não influenciam o outro. Devido a isto, o projeto dos controladores pode ser realizado separadamente apenas para um eixo e aplicado ao outro sem modificações. Neste trabalho o projeto de controle será realizado apenas no eixo  $\alpha$ .

# 3.5.1 DISCRETIZAÇÃO

De forma geral os controladores projetados para controlar os conversores estáticos são desenvolvidos no domínio do tempo contínuo e são implementados digitalmente. No entanto, esta abordagem apresenta algumas limitações (ÅSTRÖM & WITTENMARK, 2013). No projeto do controlador PI por exemplo, o método de discretização escolhido pode gerar erro de fase. Em PR os efeitos da digitalização podem degradar consideravelmente o desempenho, uma vez que algumas técnicas de discretização mudam a localização dos polos ressonantes (YEPES et al., 2010), devido ao fenômeno de distorção na frequência (frequency warping) (ÅSTRÖM & WITTENMARK, 2013).

A discretização das funções de transferência (3.27) e (3.28) foi realizada através da

estratégia Zero-order holder (ZOH) (ÅSTRÖM & WITTENMARK, 2013), cuja função de transferência no domínio z é dada por:

$$X(z) = (1 - z^{-1}) \mathscr{Z} \left[ \mathscr{L}^{-1} \left\{ \frac{X(s)}{s} \right\} \Big|_{t=kT_s} \right], \tag{3.29}$$

onde  $\mathscr{Z}$  e  $\mathscr{L}^{-1}$  são os operadores da transformada z e da transformada inversa de Laplace, respectivamente, e X(s) é a função de transferência a ser discretizada.

Substituindo os parâmetros do sistema experimental montado no Núcleo de Automação e Eletrônica de Potência (NAEP), destacados na Tabela 1, e aplicando o método ZOH para discretizar (3.27) e (3.28) têm-se que:

Tabela 1: Parâmetros do Sistema.

| Descrição                             | Valor               |

|---------------------------------------|---------------------|

| Frequência de comutação $(f_{sw})$    | 20 kHz              |

| Frequência de amostragem $(f_s)$      | 20 kHz              |

| Frequência fundamental $(f_1)$        | 60 Hz               |

| Tensão $pico$ de fase $(V_{tp})$      | 100 V               |

| Indutância do filtro de saída $(L)$   | $175~\mu\mathrm{H}$ |

| Resistência do indutor $(r_L)$        | $75 m\Omega$        |

| Capacitância do filtro de saída $(C)$ | $85 \mu F$          |

| Resistência do Capacitor $(r_C)$      | $37 m\Omega$        |

$$Z_o(z) = \frac{0.037 + 0.4988 z^{-1} - 0.5236 z^{-2}}{1 - 1.805 z^{-1} + 0.9685 z^{-2}},$$

(3.30)

e

$$G_{io}(z) = \frac{0.0921 \ z^{-1} + 0.071 \ z^{-2}}{1 - 1.805 \ z^{-1} + 0.9685 \ z^{-2}}.$$

(3.31)

### 3.6 CONCLUSÕES PARCIAS

Neste capítulo foi apresentada a modelagem do VSC na configuração de emulador de rede elétrica. Equações diferencias escritas no sistemas de coordenadas estacionário  $(\alpha\beta)$  foram usadas para modelar o comportamento dinâmico do CER. Além disso, o sistema também foi modelado no espaço de estados a fim de caracterizar o comporta-

mento do sistema no domínio da frequência.

Por fim, foi apresentada uma estratégia de discretização, utilizada para modelar o comportamento do sistema no tempo discreto.

### 4 ESTRATÉGIA DE CONTROLE

# 4.1 INTRODUÇÃO

Neste capítulo será apresentado o projeto de um controle modo de tensão com duas malhas de realimentação. A malha interna apresenta uma proposta diferente para mitigar a ressonância intrínseca do filtro LC, enquanto a malha externa garante rastreamento da tensão de referência. Inicialmente, os controladores usados nesta abordagem, serão descritos detalhadamente. Por fim, será apresentado um estudo comparativo referente ao comportamento do sistema em malha aberta e em malha fechada.

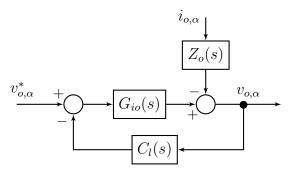

## 4.2 AMORTECIMENTO ATIVO - MALHA INTERNA DE TENSÃO

Na seção 2.3.2 foram discutidas as estratégias de amortecimento ativo mais utilizadas na literatura. Uma alternativa proposta neste trabalho para atenuar a ressonância intrínseca dos filtros de segunda ordem conectados na saída dos VSCs é ilustrada na Figura 18. A ideia se baseia na utilização de um filtro de avanço de fase na malha de realimentação da tensão.

Figura 18: Diagrama de blocos da estratégia do amortecimento ativo no tempo contínuo.

# 4.2.1 PROJETO DOS COMPENSADORES POR AVANÇO DE FASE NO TEMPO CONTÍNUO

De acordo com (MESSNER et al., 2007), a função de transferência de um compensador por avanço no tempo contínuo é dada por:

$$C_l(s) = \sqrt{\frac{\omega_p}{\omega_z}} \left( \frac{s + \omega_z}{s + \omega_p} \right), \tag{4.1}$$

em que