**UNIVERSIDADE FEDERAL DE JUIZ DE FORA**

**FACULDADE DE ENGENHARIA**

**PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA**

**Bruno Heleno da Silva**

**Controle Robusto Aplicado a *Driver* de LEDs: Otimização do Filtro

Capacitivo e Aumento da Vida Útil**

Juiz de Fora

2025

**Bruno Heleno da Silva**

**Controle Robusto Aplicado a *Driver* de LEDs: Otimização do Filtro

Capacitivo e Aumento da Vida Útil**

Tese apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Juiz de Fora como requisito parcial à obtenção do título de Doutor em Engenharia Elétrica. Área: Sistemas de Energia.

Orientador: Prof. Dr. Eng. Pedro Machado de Almeida

Coorientador: Prof. Dr. Eng. Guilherme Márcio Soares

Juiz de Fora

2025

Ficha catalográfica elaborada através do Modelo Latex do CDC da UFJF

com os dados fornecidos pelo(a) autor(a)

Silva, Bruno Heleno da.

Controle Robusto Aplicado a *Driver* de LEDs: Otimização do Filtro Capacitivo e Aumento da Vida Útil / Bruno Heleno da Silva. – 2025.

123 p. : il.

Orientador: Pedro Machado de Almeida

Coorientador: Guilherme Márcio Soares

Tese (Doutorado) – Universidade Federal de Juiz de Fora, Faculdade de Engenharia. Programa de Pós-Graduação em Engenharia Elétrica, 2025.

1. Controle robusto.

2. *Drivers* de LED.

3. Otimização  $\mathcal{H}_\infty$ .

- I. Almeida, Pedro Machado, orient. II. Soares, Guilherme Márcio, coorient. III. Título.

**Bruno Heleno da Silva**

**Controle Robusto Aplicado a Driver de LEDs:** Otimização do Filtro Capacitivo e Aumento da Vida Útil

Tese apresentada ao Programa de Pós-Graduação em Engenharia Elétrica da Universidade Federal de Juiz de Fora como requisito parcial à obtenção do título de Doutor em Engenharia Elétrica Área de concentração: Sistemas de Energia Elétrica

Aprovada em 17 de outubro de 2025.

**BANCA EXAMINADORA**

**Prof. Dr. Pedro Machado de Almeida** - Orientador

Universidade Federal de Juiz de Fora

**Prof. Dr. Guilherme Márcio Soares** - Coorientador

Universidade Federal de Juiz de Fora

**Prof. Dr. Henrique Antônio Carvalho Braga**

Universidade Federal de Juiz de Fora

**Prof. Dr. Pedro Santos Almeida**

Universidade Federal de Juiz de Fora

**Prof. Dr. Fernando Luiz Marcelo Antunes**

Universidade Federal do Ceará

**Prof. Dr. Luiz Antonio Maccari Junior**

Universidade Federal de Santa Catarina

Juiz de Fora, 18/09/2025.

Documento assinado eletronicamente por **Fernando Luiz Marcelo Antunes**, Usuário Externo, em 22/09/2025, às 09:34, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do Decreto nº 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por **Pedro Machado de Almeida, Professor(a)**, em 17/10/2025, às 12:45, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do Decreto nº 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por **Guilherme Márcio Soares, Professor(a)**, em 17/10/2025, às 13:47, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do Decreto nº 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por **Henrique Antonio Carvalho Braga, Professor(a)**, em 17/10/2025, às 15:42, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do Decreto nº 10.543, de 13 de novembro de 2020.

Documento assinado eletronicamente por **Luiz Antonio Maccari Jr., Usuário Externo**, em 20/10/2025, às 07:13, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do Decreto nº 10.543, de 13 de novembro de 2020.

de 2020.

Documento assinado eletronicamente por **Pedro Santos Almeida, Professor(a)**, em 28/11/2025, às 14:40, conforme horário oficial de Brasília, com fundamento no § 3º do art. 4º do [Decreto nº 10.543, de 13 de novembro de 2020](#).

A autenticidade deste documento pode ser conferida no Portal do SEI-Ufjf ([www2.ufjf.br/SEI](http://www2.ufjf.br/SEI)) através do ícone Conferência de Documentos, informando o código verificador **2625636** e o código CRC **0190B851**.

*Dedico este trabalho aos meus pais, Heleno e Maristela.*

## **AGRADECIMENTOS**

Ao meu orientador, Prof. Dr. Eng. Pedro Machado de Almeida pela orientação, ensinamentos, amizade, atenção e paciência durante todo o desenvolvimento deste trabalho.

Ao meu coorientador, Prof. Dr. Eng. Guilherme Márcio Soares, pela disponibilidade e colaboração para que este trabalho pudesse ser realizado.

Aos meus pais, pelo apoio incondicional que me deram nesta caminhada, me dando forças, carinho e amor para prosseguir.

Aos amigos de longa data, Ruan Ferraz e Lucas Resende, aos que eu adquiri ao longo deste trabalho, Pedro Henrique e Tamires pela ajuda e convívio neste período. Em especial, ao amigo Josué Lima pela ajuda para superar os obstáculos que apareceram no decorrer deste trabalho, disponibilidade e convívio no NIMO.

Aos meus amigos que sempre torcem por mim.

A FAPEMIG, à Universidade Federal de Juiz de Fora e à Faculdade de Engenharia pelo suporte financeiro e por prover as ferramentas necessárias para o desenvolvimento deste trabalho.

*“Educação não transforma o mundo. Educação muda pessoas. Pessoas transformam o mundo.”*

(Paulo Freire).

## RESUMO

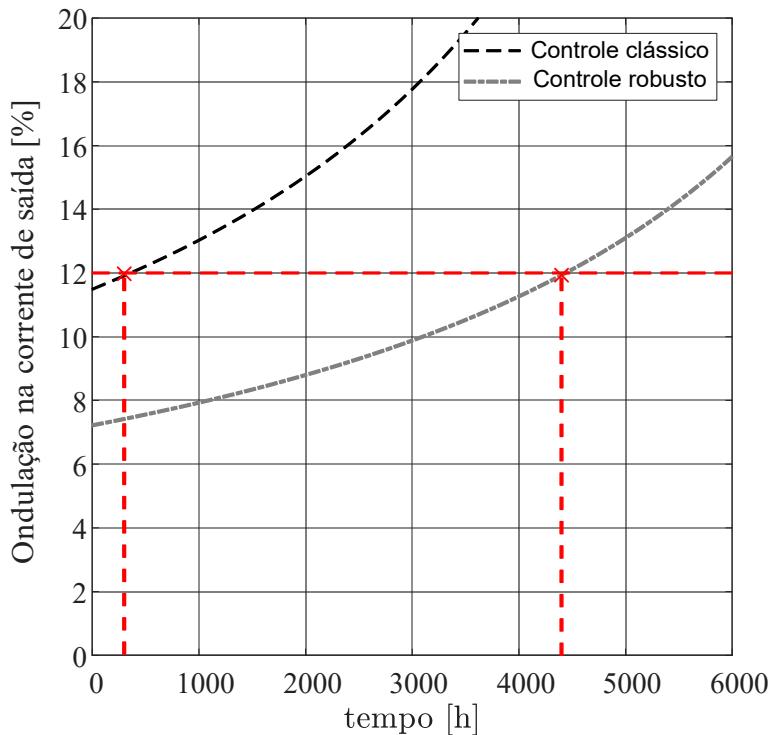

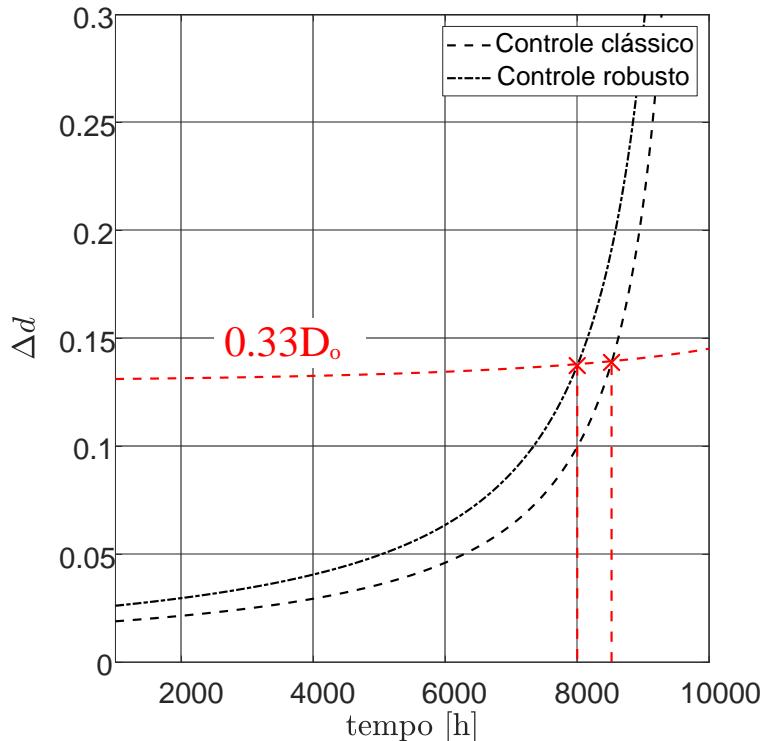

Este trabalho propõe duas aplicações de controle robusto em *drivers* de diodos emissores de luz (LEDs), visando melhorias na eficiência e na vida útil desses sistemas. A primeira proposta foca na redução do filtro capacitivo por meio da técnica de otimização  $\mathcal{H}_\infty$ . Em dispositivos de *drivers* de LEDs, o uso de capacitores de alta capacidade é comum, porém isso pode resultar em taxas elevadas de falhas, prejudicando a confiabilidade do sistema. A segunda proposta visa prolongar a vida útil do *driver* através do controle robusto diante do processo de degradação do capacitor eletrolítico ao longo do tempo. O *driver* escolhido para estas propostas é um conversor buck-boost flyback, projetado para alto fator de potência e conformidade com normas, operando em uma faixa de tensão universal de 90 a 264 V e potência máxima de 75 W. O controle é implementado com realimentação de estados robusta, utilizando ganhos determinados por desigualdades matriciais lineares (LMIs), garantindo estabilidade em diferentes pontos de operação dinâmicos. Ambas as propostas se baseiam no controle ativo, que minimiza a transferência de ondações do barramento para a saída, mantendo requisitos mínimos de qualidade de energia para uma eficiente operação do *driver*. A otimização  $\mathcal{H}_\infty$  é empregada para minimizar distúrbios, sendo implementada por LMIs. No entanto, a estratégia de controle ativo enfrenta limitações devido à distorção da corrente de entrada. Essas limitações são superadas com restrições no cálculo dos ganhos do controlador, assegurando a ondação desejada na corrente de saída e o conteúdo harmônico da corrente de entrada conforme normas. Além disso, uma limitação no parâmetro proporcional do controlador é implementada para evitar a amplificação de ruídos indesejáveis. Como resultado da aplicação dessas metodologias, observou-se uma redução expressiva de aproximadamente 70% no filtro capacitivo do *driver* na primeira proposta. Já na segunda proposta, houve um aumento significativo de 4100 h na vida útil do sistema. Em ambas as abordagens, os requisitos mínimos de qualidade de energia e ondação na corrente de saída foram mantidos.

Palavras-chave: Controle robusto. *Drivers* de LED. Otimização  $\mathcal{H}_\infty$ .

## ABSTRACT

This work proposes two applications of robust control in LED drivers, aiming to improve efficiency and lifespan of these systems. The first proposal focuses on reducing the capacitive filter through the  $\mathcal{H}_\infty$  optimization technique. In LED driver devices, the use of high-capacitance capacitors is common, but this can result in high failure rates, compromising system reliability. The second proposal aims to extend the lifespan of the driver through robust control in the face of electrolytic capacitor degradation over time. The chosen driver for these proposals is a buck-boost flyback converter, designed for high power factor and compliance with standards, operating in a universal voltage range of 90 to 264 V and 75 W maximum power. Control is implemented with robust state feedback, using gains determined by LMIs, ensuring stability at different dynamic operating points. Both proposals are based on active control, which minimizes the transfer of bus ripples to the output, while maintaining minimum energy quality requirements for efficient driver operation. The  $\mathcal{H}_\infty$  optimization is employed to minimize disturbances, implemented by LMIs. However, the active control strategy faces limitations due to input current distortion. These limitations are overcome with restrictions on controller gain calculation, ensuring desired output ripple and harmonic content of the input current according to standards. Additionally, a limitation on the proportional parameter of the controller is implemented to avoid amplification of unwanted noise. As a result of the application of these methodologies, a significant reduction of approximately 70% in the driver's capacitive filter was observed in the first proposal. In the second proposal, there was a significant increase of 4100 h in the system's lifespan. In both approaches, minimum energy quality requirements and output current ripple were maintained.

Keywords: Robust control. LED drivers.  $\mathcal{H}_\infty$  optimization.

## LISTA DE ILUSTRAÇÕES

|           |                                                                                                                                                                                                                                                                                                                                                                                                                               |    |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1  | – Participação de LEDs nas vendas globais de iluminação (pontos selecionados) e marco NZE da IEA (100% de vendas em LED até 2025). . . . .                                                                                                                                                                                                                                                                                    | 16 |

| Figura 2  | – <i>Driver</i> de dois estágios. . . . .                                                                                                                                                                                                                                                                                                                                                                                     | 17 |

| Figura 3  | – Forma de onda da corrente no LED. . . . .                                                                                                                                                                                                                                                                                                                                                                                   | 18 |

| Figura 4  | – Taxa de falhas em capacitores ao longo do tempo. . . . .                                                                                                                                                                                                                                                                                                                                                                    | 19 |

| Figura 5  | – Taxa de falhas em função da capacitância. . . . .                                                                                                                                                                                                                                                                                                                                                                           | 20 |

| Figura 6  | – Comparação entre volume e densidade de carga de capacitores de filme e eletrolíticos. (a) Capacitor de filme de 22 $\mu\text{F}$ e 100 V – 10,5 $\text{cm}^3$ . (b) Capacitor eletrolítico de 22 $\mu\text{F}$ e 160 V – 5,3 $\text{cm}^3$ . (c) Capacitor de filme de 2,2 $\mu\text{F}$ e 400 V – 10,5 $\text{cm}^3$ . (d) Capacitor eletrolítico de 2,2 $\mu\text{F}$ e 450 V – 4,1 $\text{cm}^3$ . Régua em centímetros. | 20 |

| Figura 7  | – Circuito equivalente do capacitor eletrolítico. . . . .                                                                                                                                                                                                                                                                                                                                                                     | 21 |

| Figura 8  | – Compensação da ondulação através de um conversor bidirecional. . . . .                                                                                                                                                                                                                                                                                                                                                      | 25 |

| Figura 9  | – Conexão entre os estágios de potência de forma otimizada.                                                                                                                                                                                                                                                                                                                                                                   | 25 |

| Figura 10 | – PFC com indutor acoplado e regulador CA-CC. . . . .                                                                                                                                                                                                                                                                                                                                                                         | 26 |

| Figura 11 | – Controle da corrente de entrada distorcida. . . . .                                                                                                                                                                                                                                                                                                                                                                         | 27 |

| Figura 12 | – Compensação ativa da ondulação. . . . .                                                                                                                                                                                                                                                                                                                                                                                     | 28 |

| Figura 13 | – Sistema em malha aberta. . . . .                                                                                                                                                                                                                                                                                                                                                                                            | 33 |

| Figura 14 | – Sistema aumentado em malha fechada. . . . .                                                                                                                                                                                                                                                                                                                                                                                 | 35 |

| Figura 15 | – Região determinada para alocação dos polos. . . . .                                                                                                                                                                                                                                                                                                                                                                         | 41 |

| Figura 16 | – <i>Driver</i> implementado. . . . .                                                                                                                                                                                                                                                                                                                                                                                         | 43 |

| Figura 17 | – Modelo linear da carga LED. . . . .                                                                                                                                                                                                                                                                                                                                                                                         | 44 |

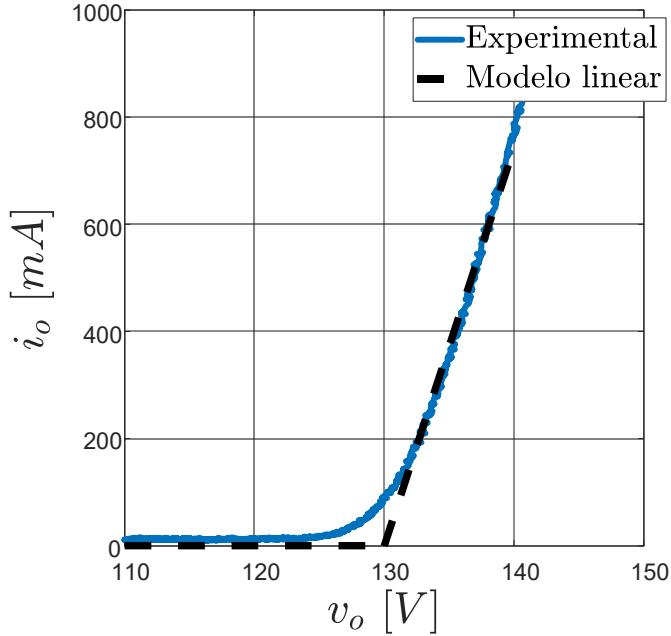

| Figura 18 | – Modelo linear e resultado experimental da carga LED. . .                                                                                                                                                                                                                                                                                                                                                                    | 45 |

| Figura 19 | – Diagrama de blocos para perturbações de pequenos sinais do conversor integrado. . . . .                                                                                                                                                                                                                                                                                                                                     | 48 |

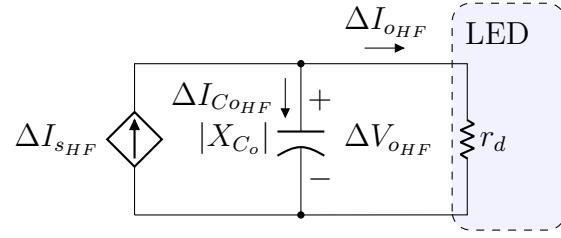

| Figura 20 | – Circuito equivalente do segundo estágio. . . . .                                                                                                                                                                                                                                                                                                                                                                            | 48 |

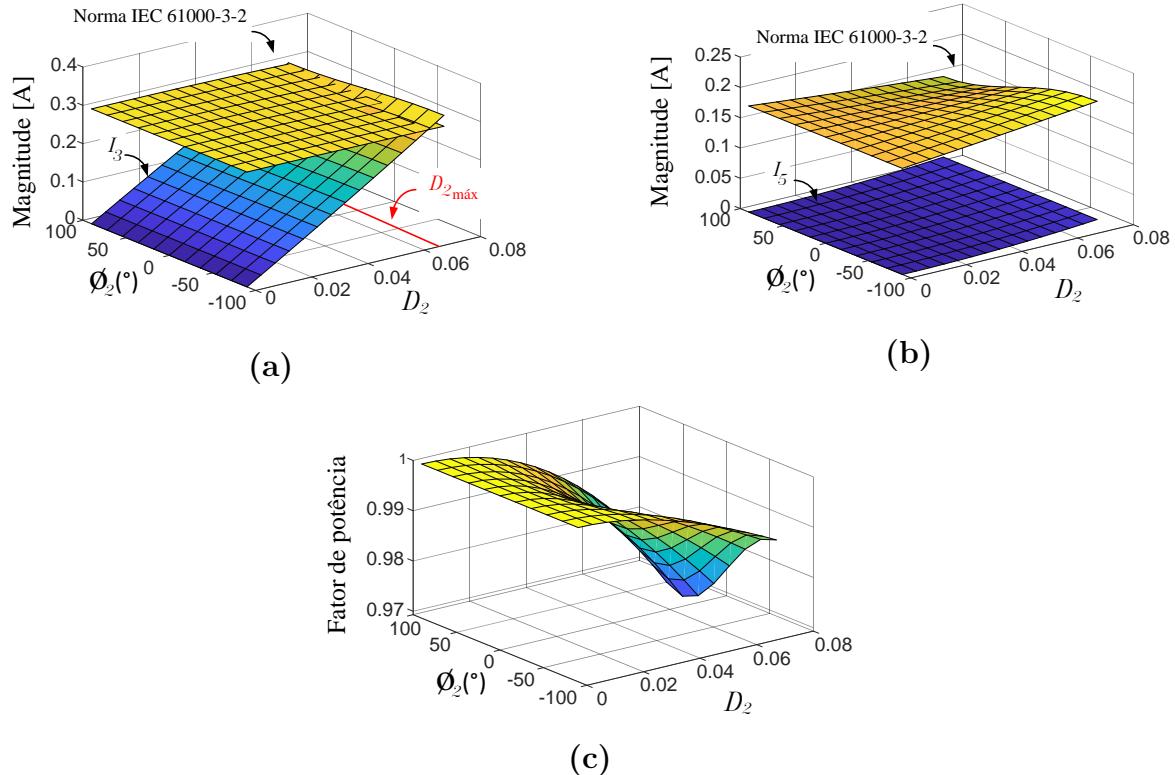

| Figura 21 | – Conteúdo harmônico da corrente de entrada de acordo com a aproximação teórica da razão cíclica em 90 V e 50 Hz: (a) terceiro harmônico, (b) quinto harmônico e (c) fator de potência. .                                                                                                                                                                                                                                     | 55 |

| Figura 22 | – Circuito equivalente do segundo estágio em alta frequência.                                                                                                                                                                                                                                                                                                                                                                 | 59 |

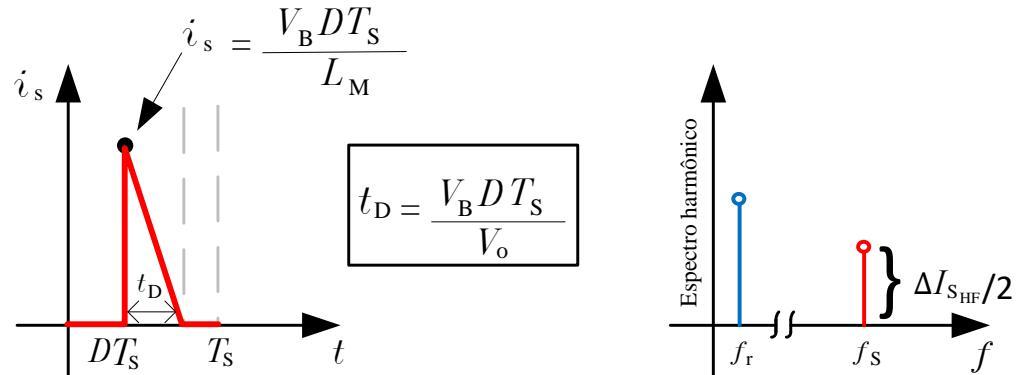

| Figura 23 | – Corrente no secundário do transformador em alta frequência.                                                                                                                                                                                                                                                                                                                                                                 | 59 |

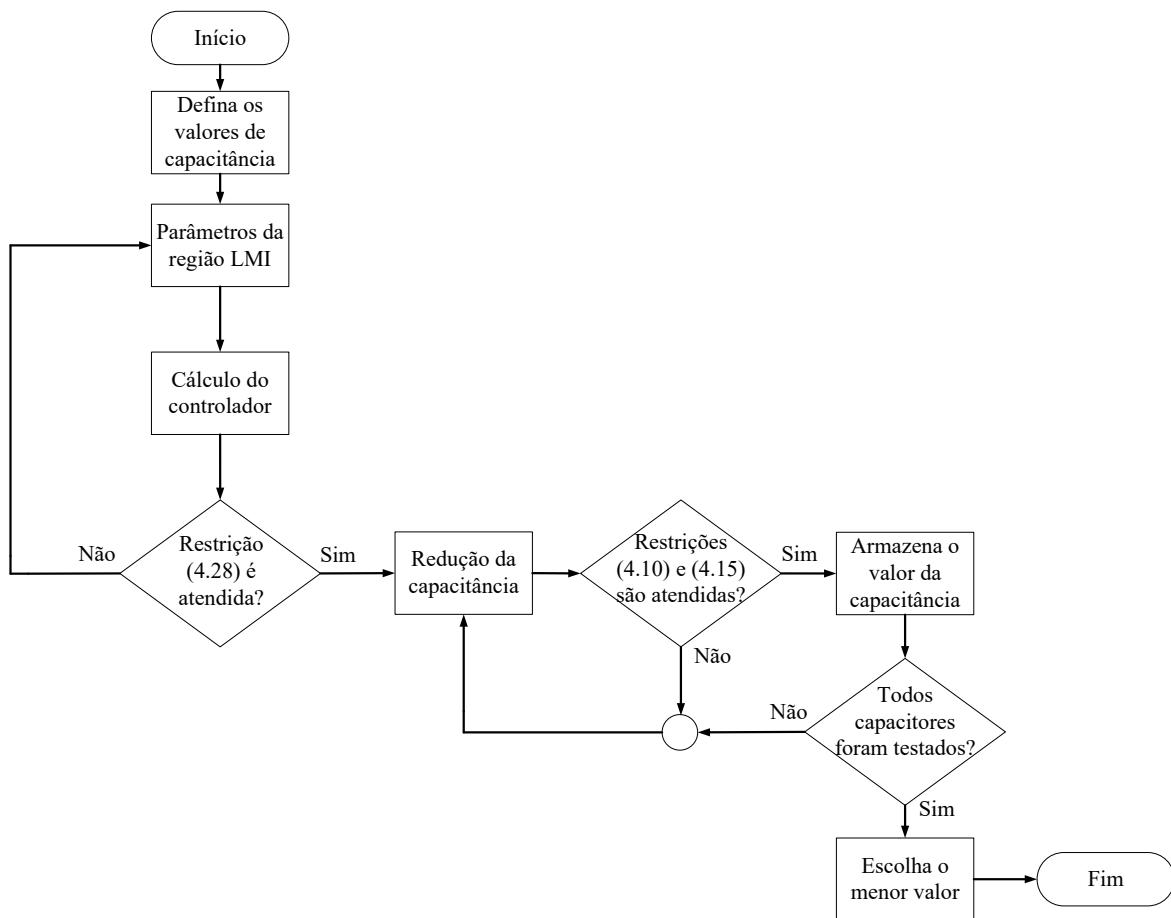

| Figura 24 | – Fluxograma da metodologia de redução do filtro capacitivo.                                                                                                                                                                                                                                                                                                                                                                  | 61 |

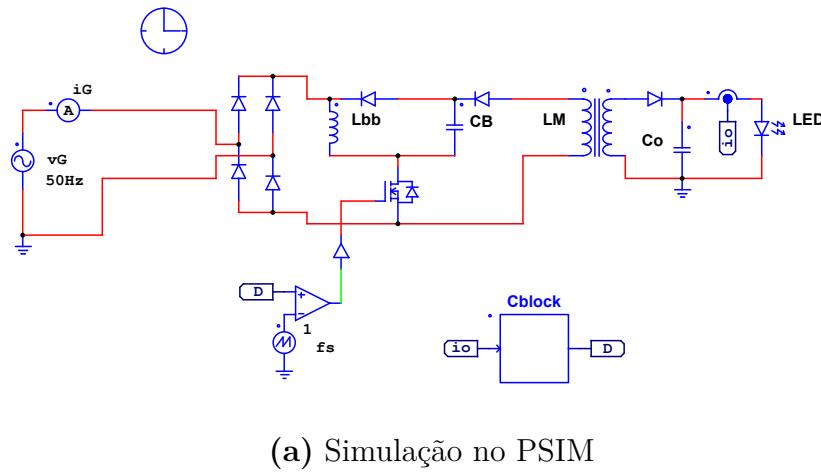

| Figura 25 | – Circuito utilizado na validação: (a) configuração para simulação e (b) protótipo para experimento. . . . .                                                                                                                                                                                                                                                                                                                  | 62 |

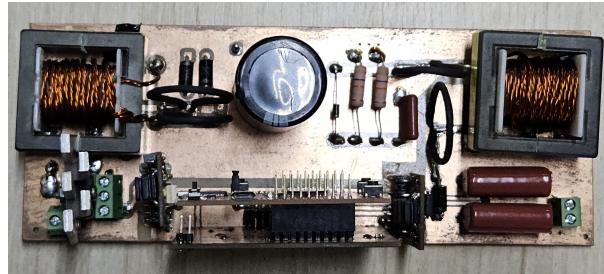

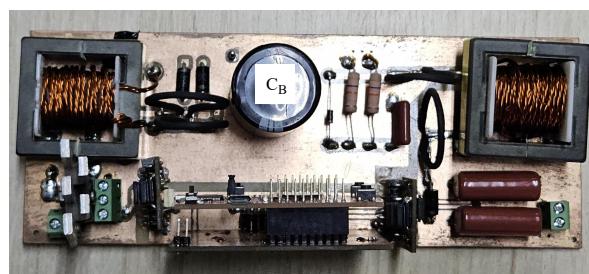

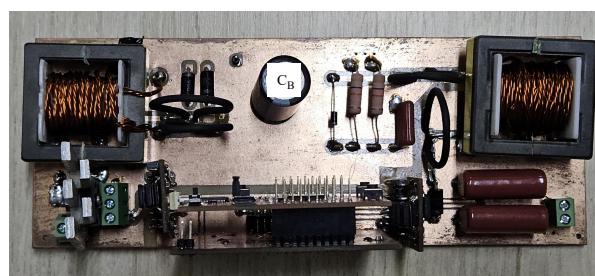

| Figura 26 | – Protótipo com (a) capacitor nominal e (b) capacitor reduzido.                                                                                                                                                                                                                                                                                                                                                               | 65 |

|           |                                                                                                                                                                                       |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

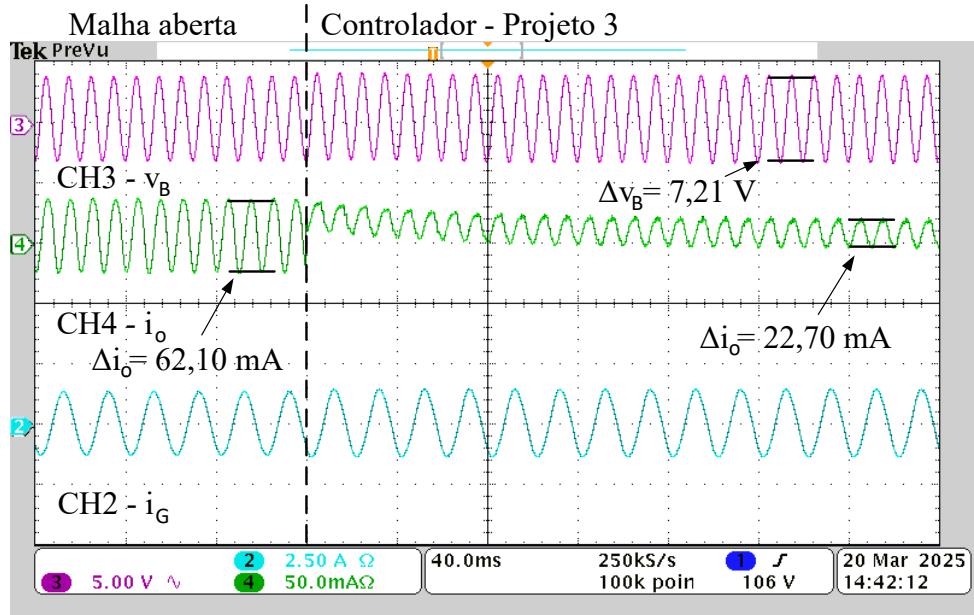

| Figura 27 | – Implementação do controlador “Projeto 3” com $C_B = 330 \mu\text{F}$ na tensão de entrada de 90 V e 50 Hz. . . . .                                                                  | 67 |

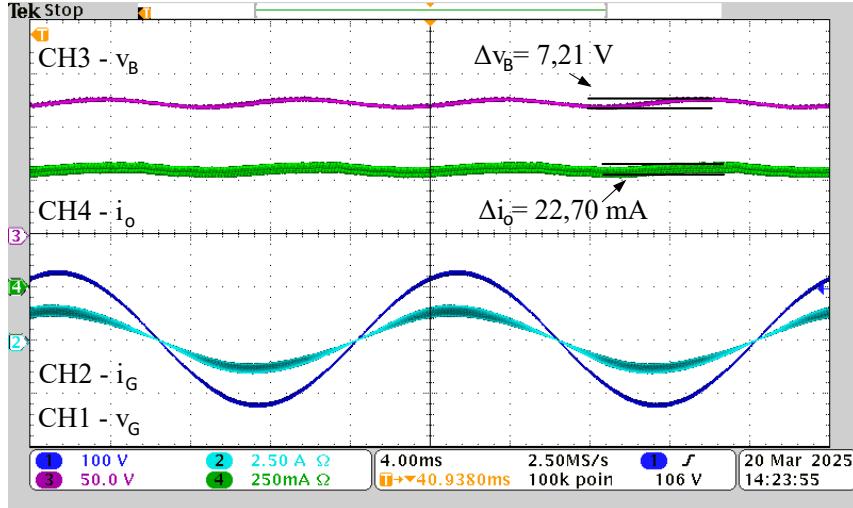

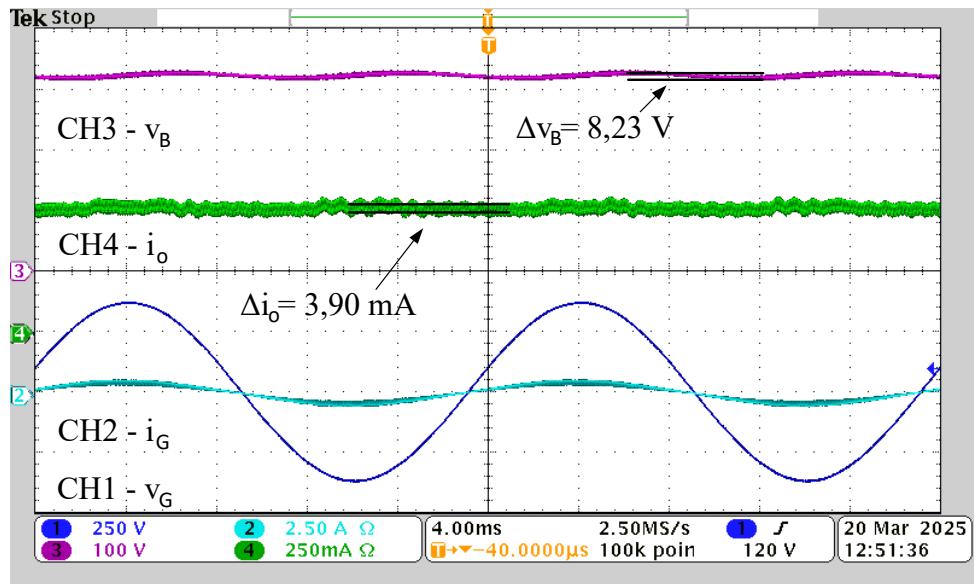

| Figura 28 | – Comparação entre as formas de onda experimentais utilizando o controlador $\mathcal{H}_\infty$ em 90 V e 50 Hz. (a) Com capacitor nominal e (b) com capacitor reduzido. . . . .     | 68 |

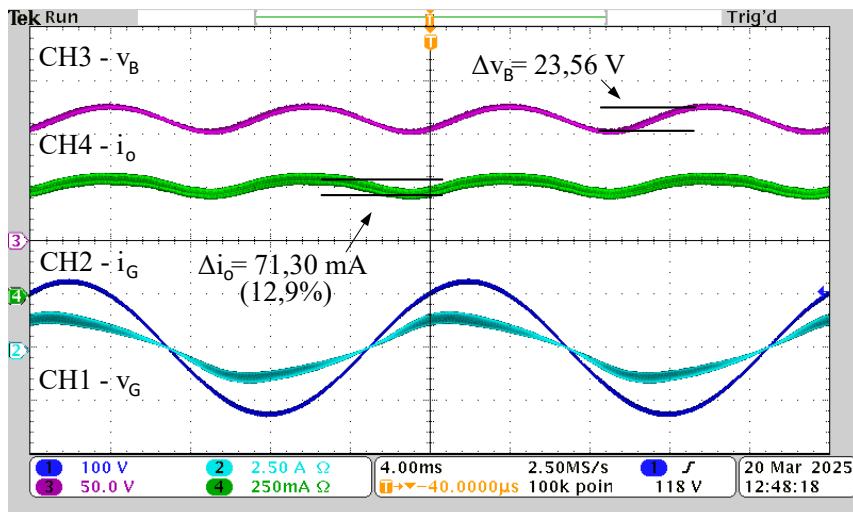

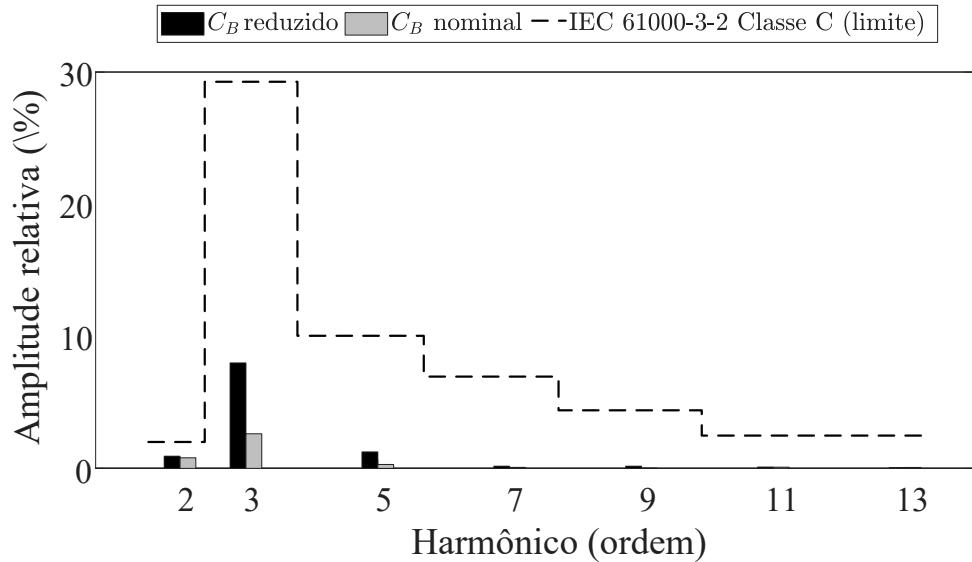

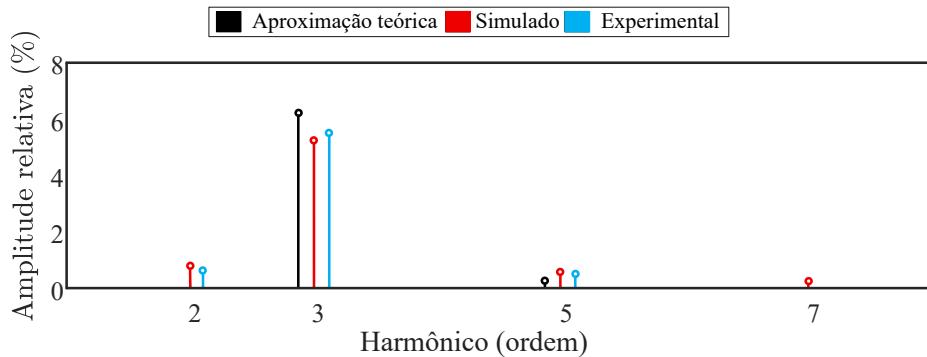

| Figura 29 | – Conteúdo harmônico da corrente de entrada com capacitor nominal ( $330 \mu\text{F}$ ) e reduzido ( $100 \mu\text{F}$ ) em 90 V e 50 Hz. . . . .                                     | 69 |

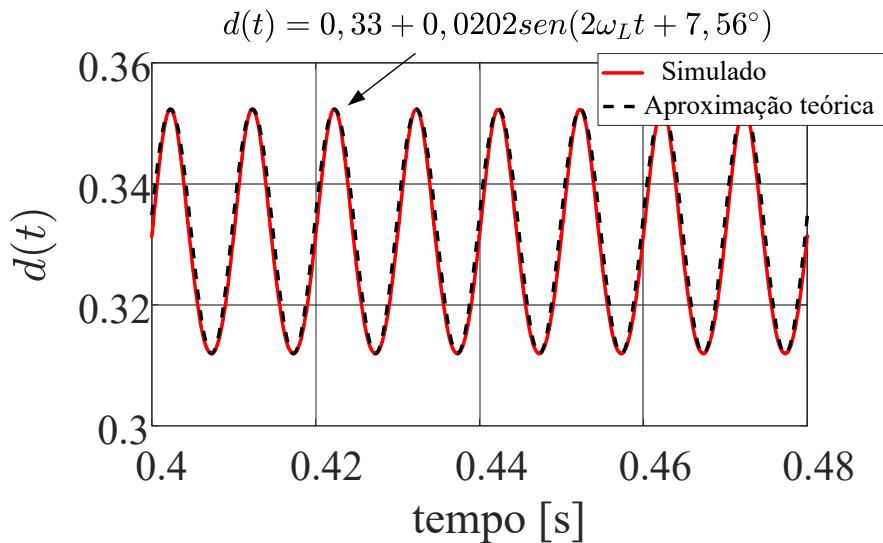

| Figura 30 | – Comparação entre a aproximação teórica e a forma de onda simulada da razão cíclica em 90 V e 50 Hz. . . . .                                                                         | 69 |

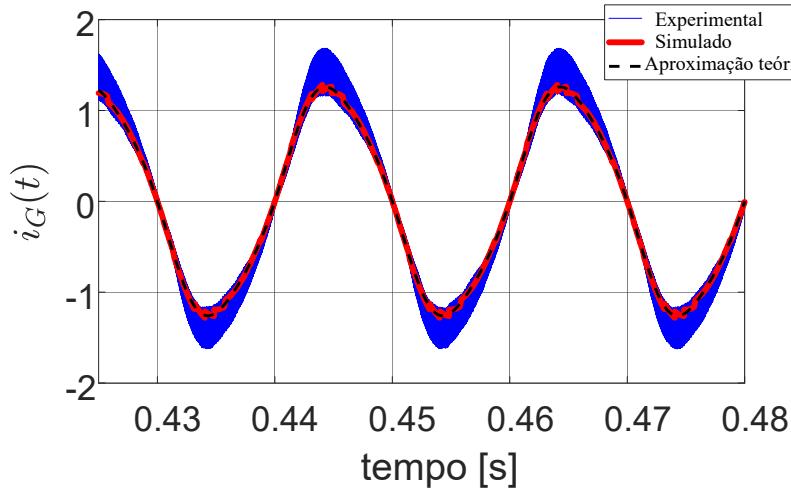

| Figura 31 | – Comparação entre a aproximação teórica, a simulação e a medição experimental da corrente de entrada em 90 V e 60 Hz com capacitor reduzido. . . . .                                 | 70 |

| Figura 32 | – Principais formas de onda experimentais com capacitor reduzido em 264 V e 50 Hz. . . . .                                                                                            | 71 |

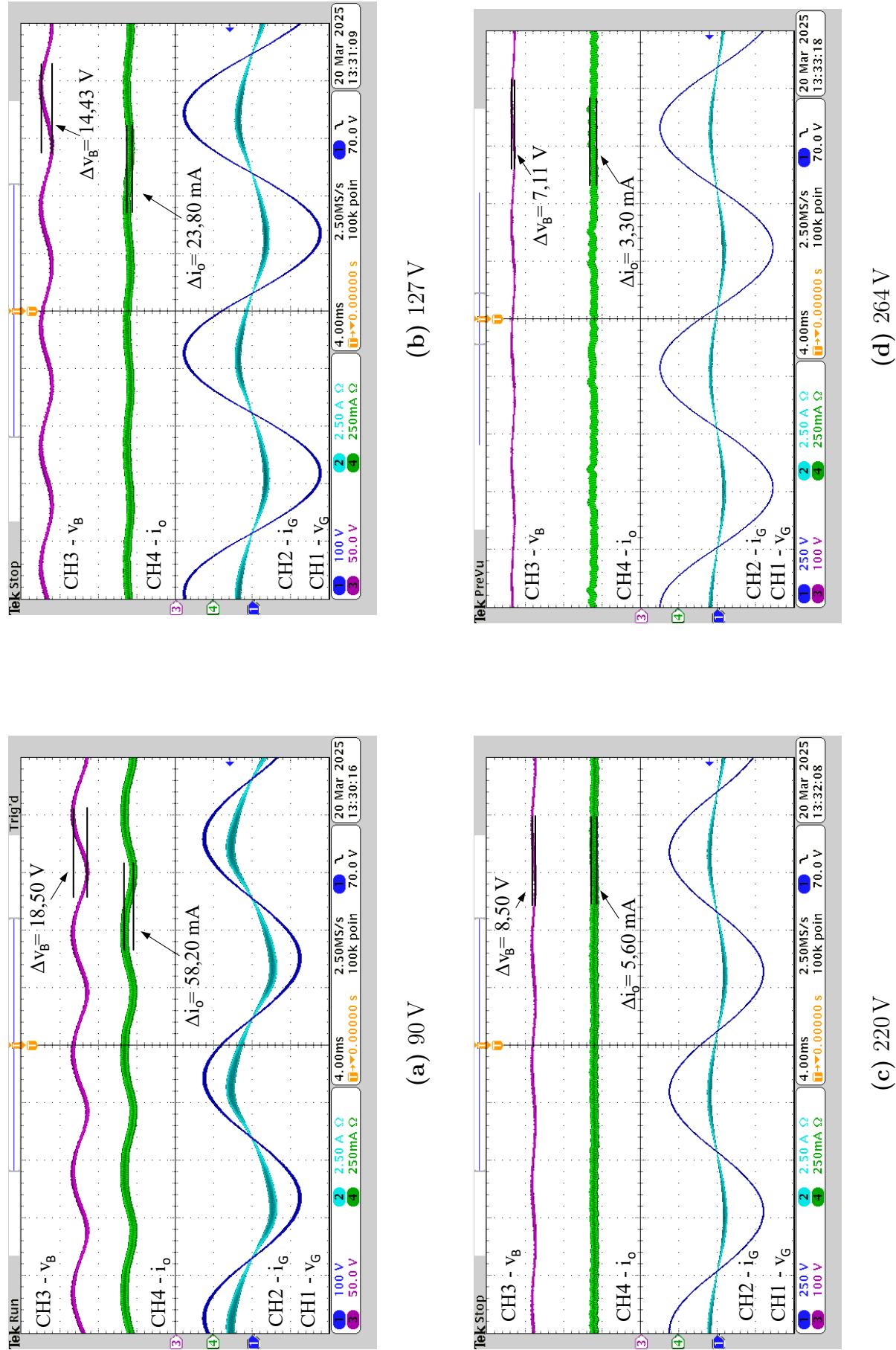

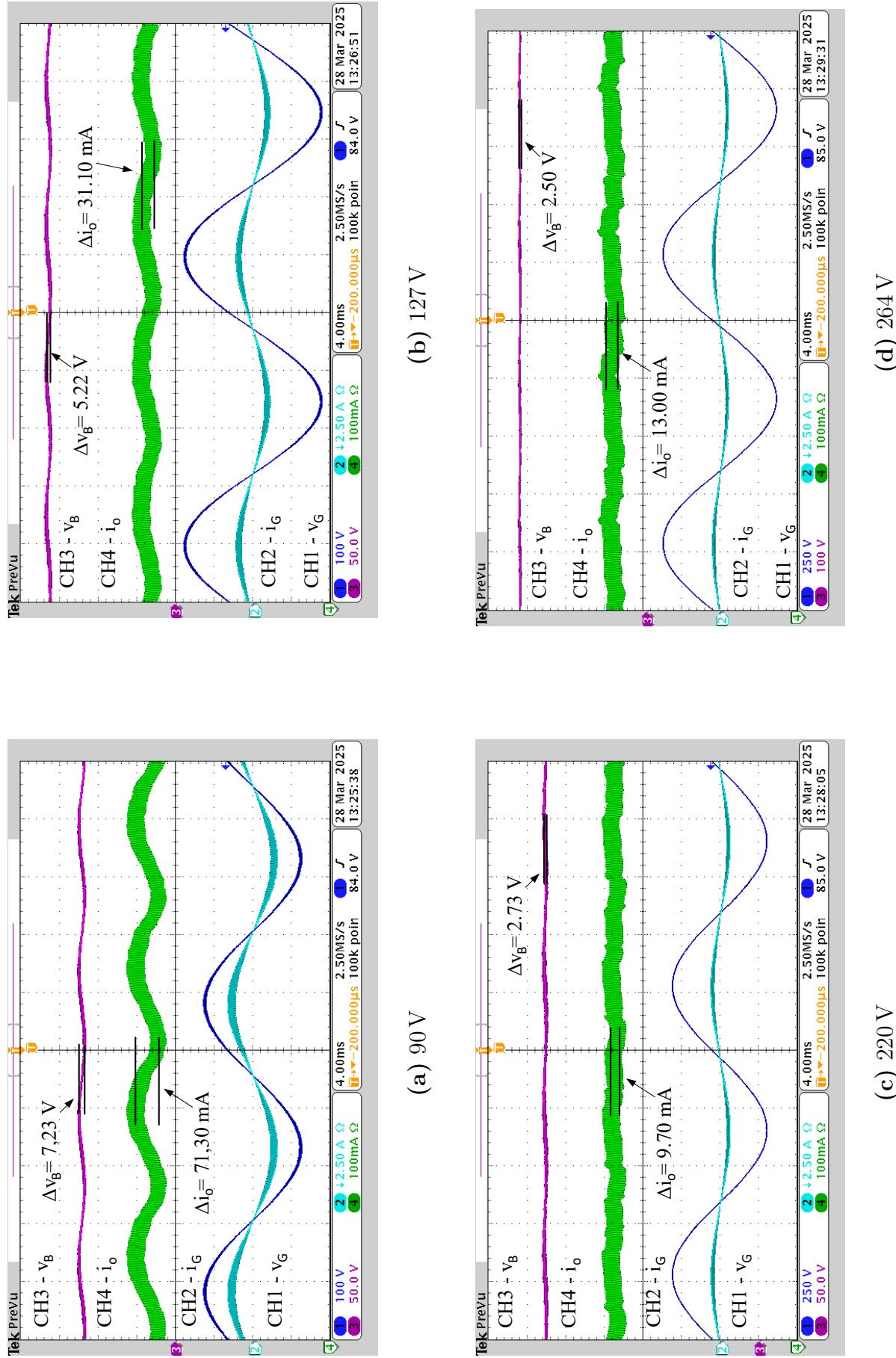

| Figura 33 | – Formas de onda com capacitor reduzido ( $100 \mu\text{F}$ ) em 50 Hz. .                                                                                                             | 72 |

| Figura 34 | – Formas de onda com capacitor reduzido ( $100 \mu\text{F}$ ) em 60 Hz. .                                                                                                             | 73 |

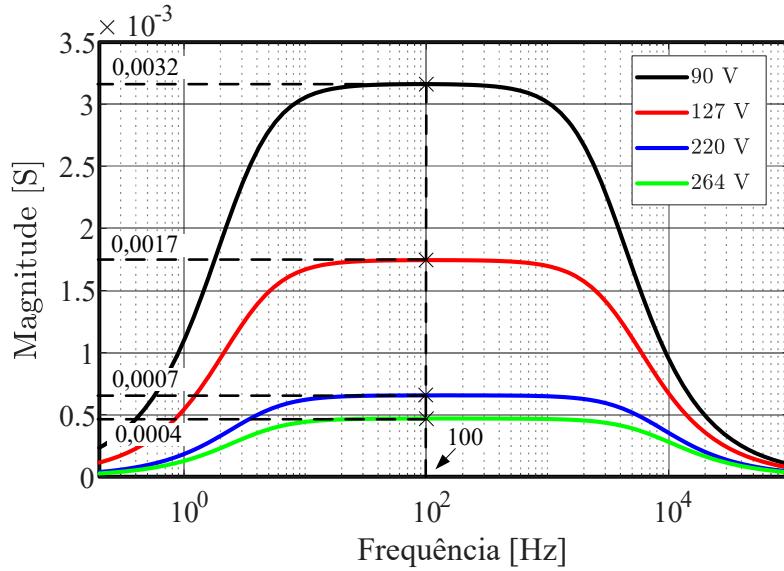

| Figura 35 | – Resposta em frequência de malha fechada de $G_{iv}$ utilizando a norma $\mathcal{H}_\infty$ na tensão de entrada em 90 V e 50 Hz. . . . .                                           | 74 |

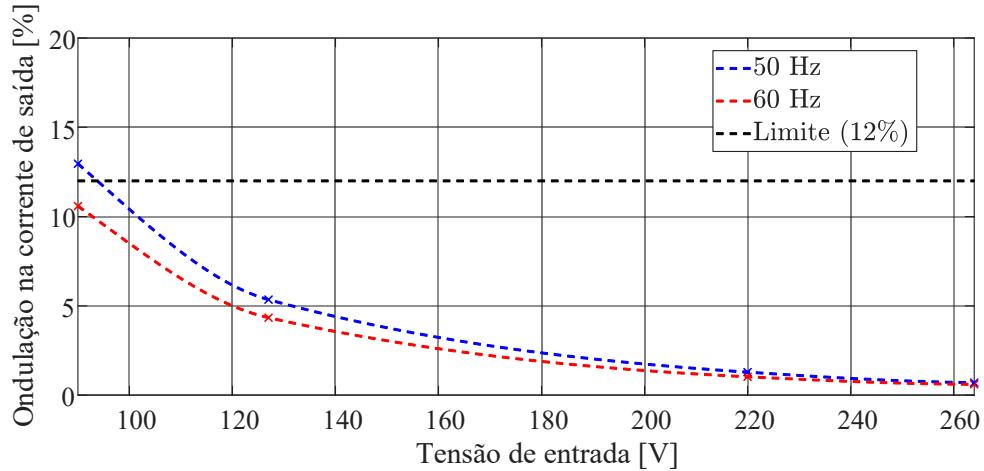

| Figura 36 | – Comparação da ondulação da corrente de saída em 50 Hz e 60 Hz para uma tensão de entrada de 90 V. . . . .                                                                           | 74 |

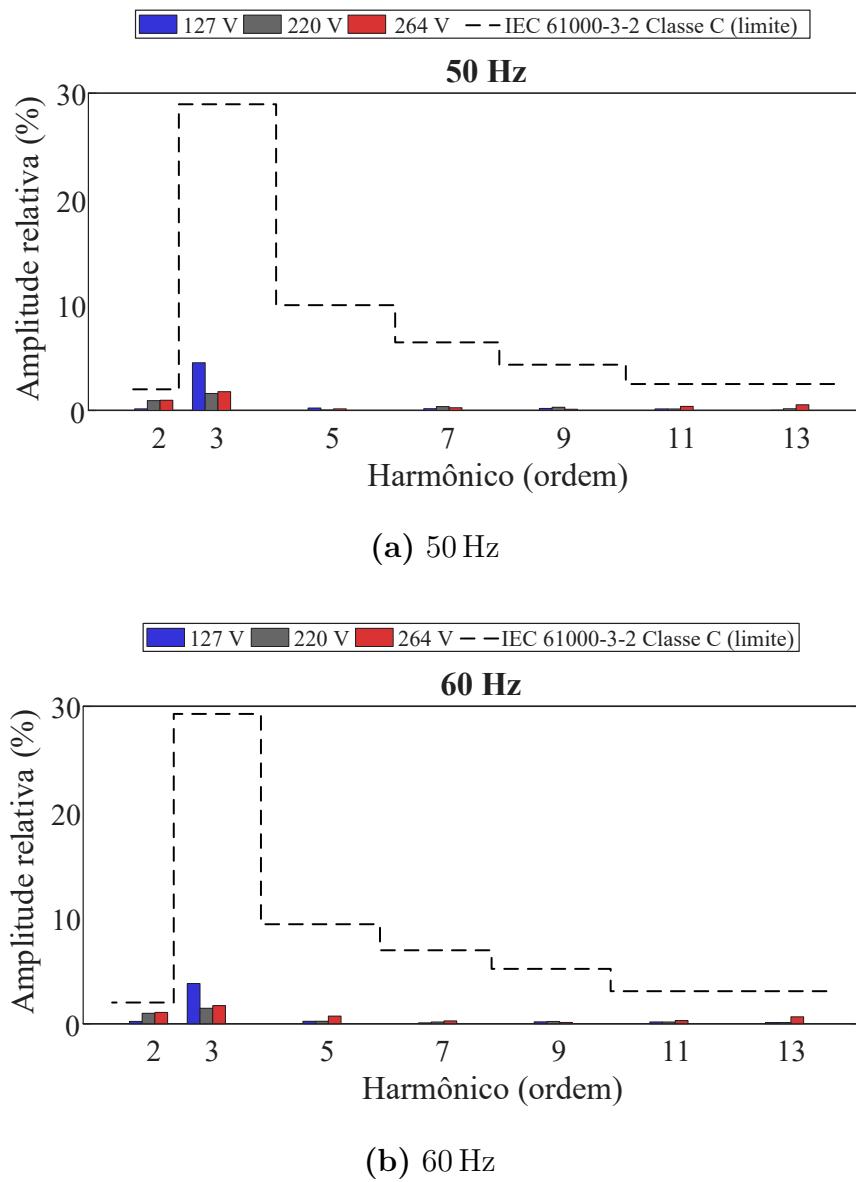

| Figura 37 | – Comparação entre o conteúdo harmônico da corrente de entrada com os limites da norma IEC na tensão de 127 V, 220 V e 264 V com capacitor reduzido em (a) 50 Hz e (b) 60 Hz. . . . . | 75 |

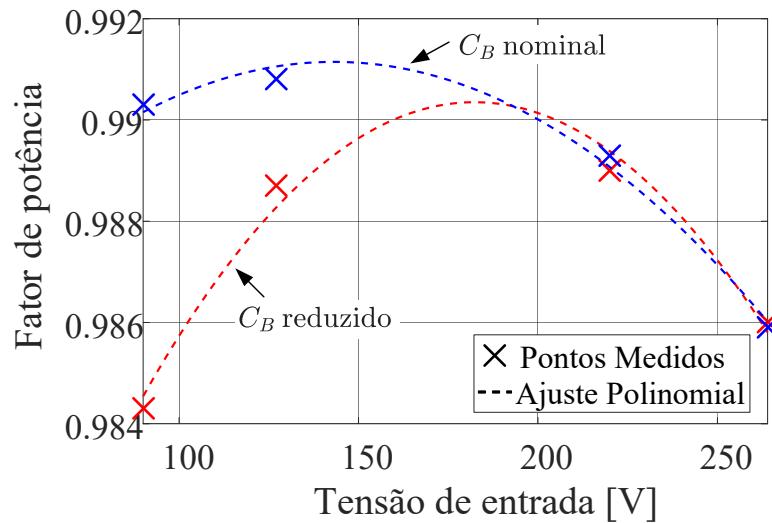

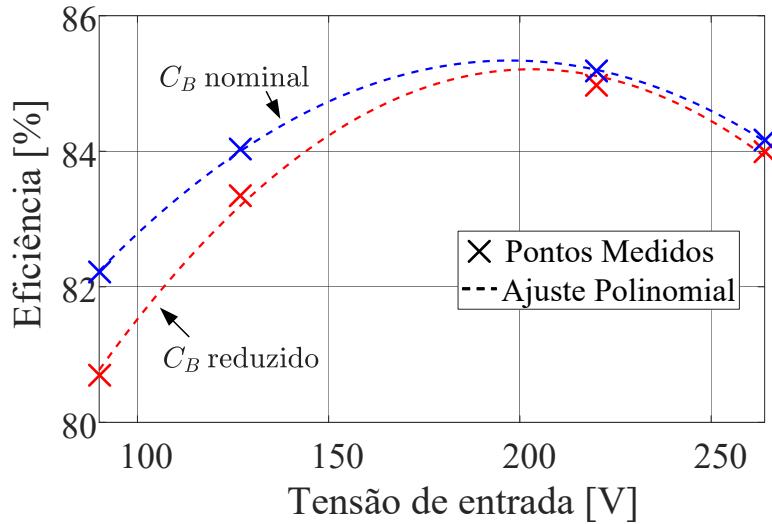

| Figura 38 | – Fator de potência e $THD$ em função da tensão de entrada em 50 Hz. . . . .                                                                                                          | 76 |

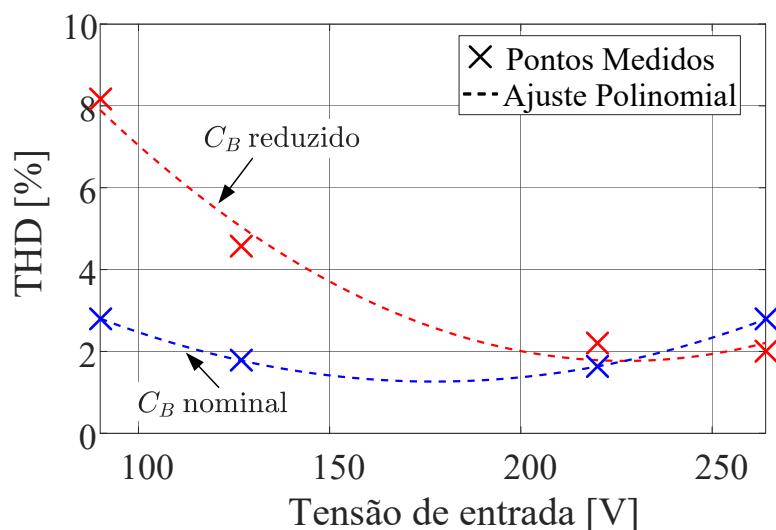

| Figura 39 | – Eficiência do conversor em função da tensão de entrada em 50 Hz. . . . .                                                                                                            | 77 |

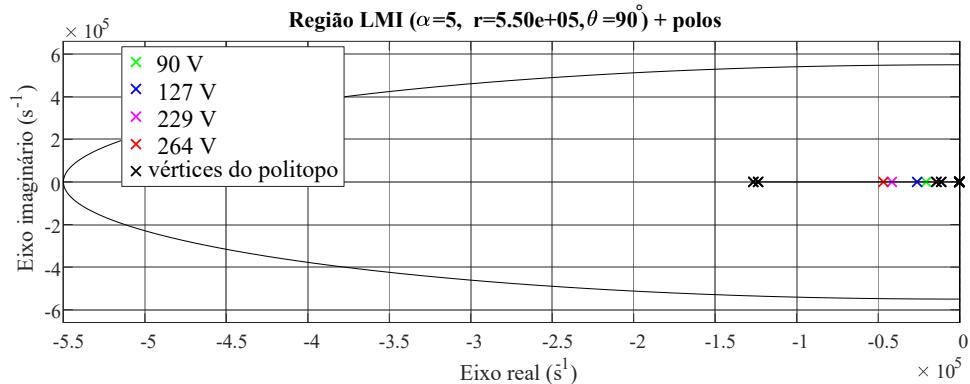

| Figura 40 | – Localização da região polítónica de incertezas. . . . .                                                                                                                             | 77 |

| Figura 41 | – Comportamento transitório sob dimerização em diferentes pontos de operação. . . . .                                                                                                 | 78 |

| Figura 42 | – Comparação entre formas de onda experimentais e simuladas sob degraus de referência. . . . .                                                                                        | 79 |

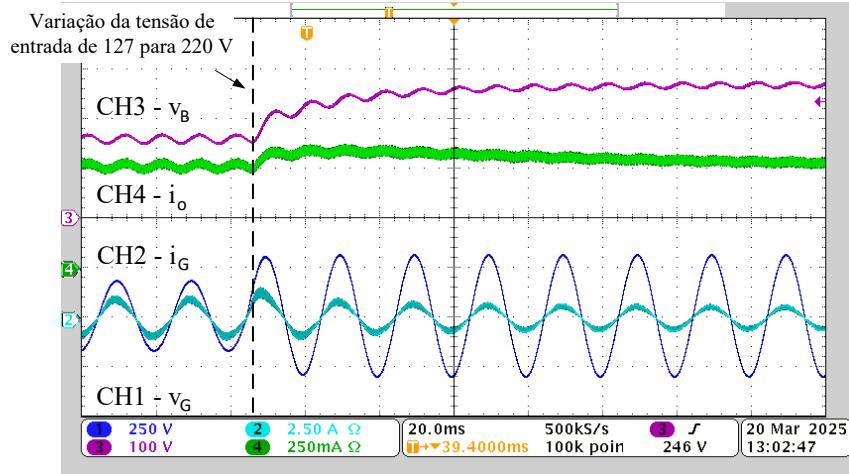

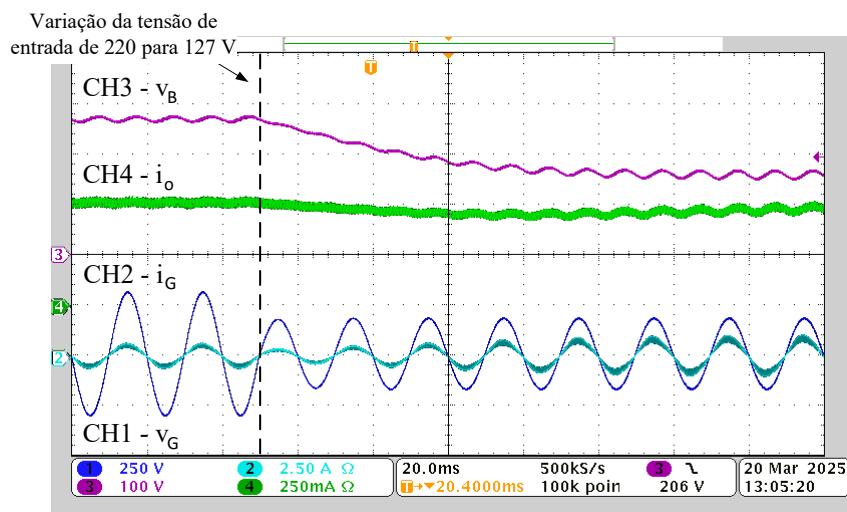

| Figura 43 | – Distúrbio na tensão de entrada: (a) de 127 V para 220 V eficaz e (b) de 220 V para 127 V eficaz. . . . .                                                                            | 80 |

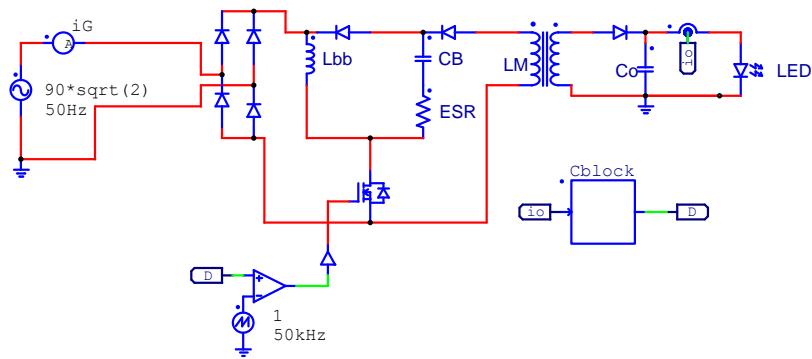

| Figura 44 | – Circuito utilizado em simulação considerando a ESR. . . . .                                                                                                                         | 82 |

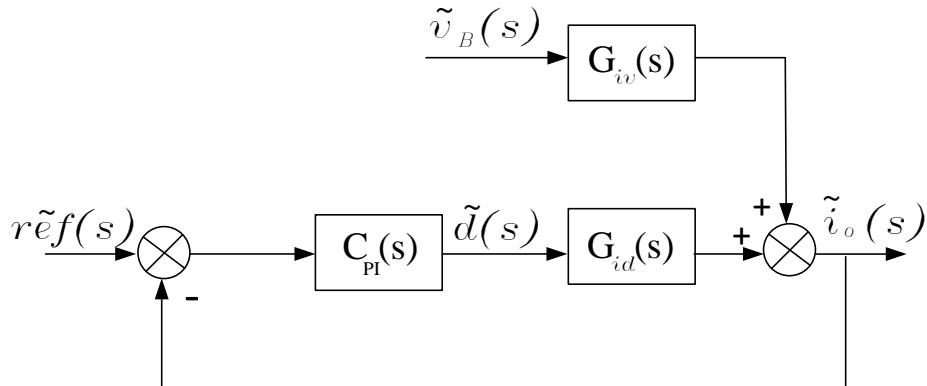

| Figura 45 | – Malha com o controlador proporcional-integral. . . . .                                                                                                                              | 83 |

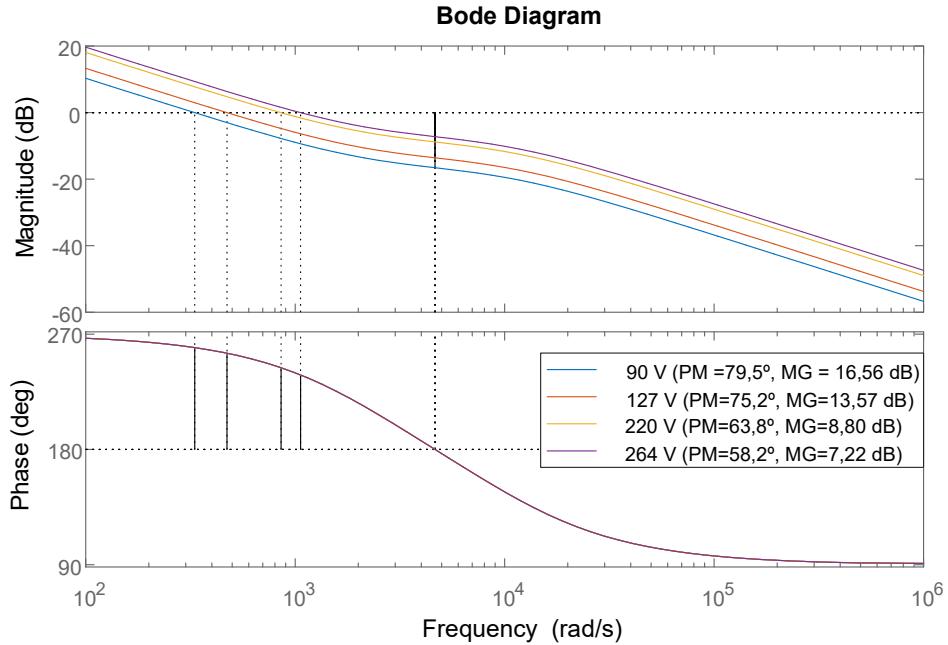

| Figura 46 | – Diagrama de Bode do sistema compensado. . . . .                                                                                                                                     | 85 |

| Figura 47 | – Ondulação na corrente de saída diante do processo de degradação do capacitor. . . . .                                                                                               | 86 |

|           |                                                                                                                                                                                       |     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 48 | – Amplitude da razão cíclica diante do processo de degradação do capacitor. . . . .                                                                                                   | 87  |

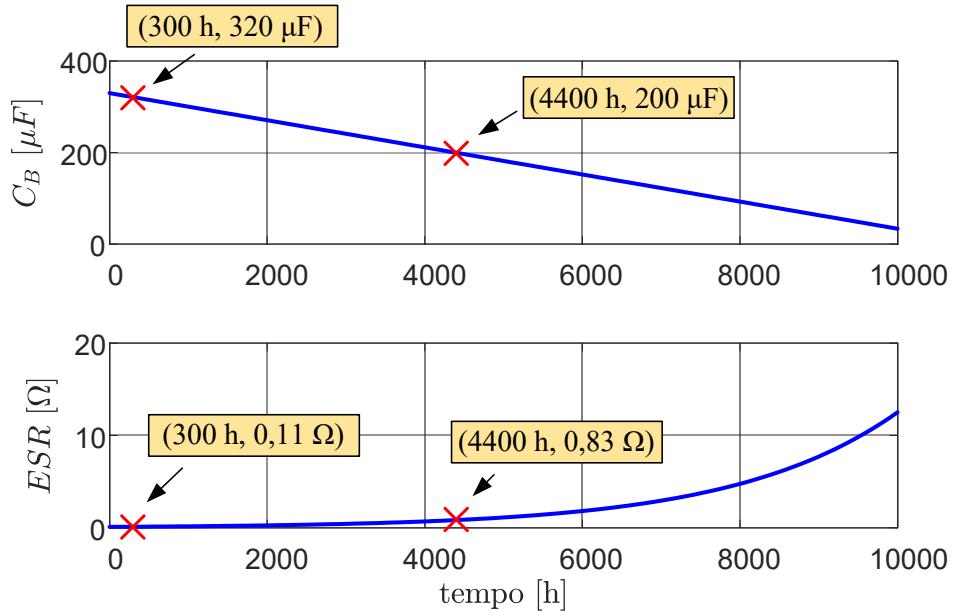

| Figura 49 | – Modelo de degradação do capacitor eletrolítico a 105 °C. . . . .                                                                                                                    | 88  |

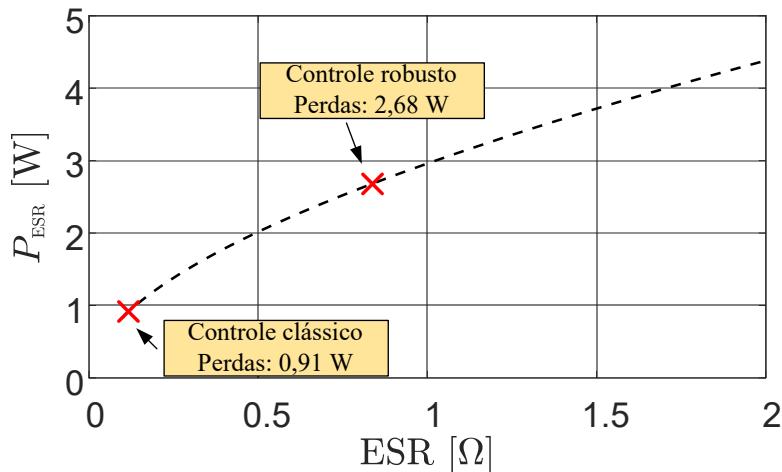

| Figura 50 | – Estimativa das perdas na ESR. . . . .                                                                                                                                               | 88  |

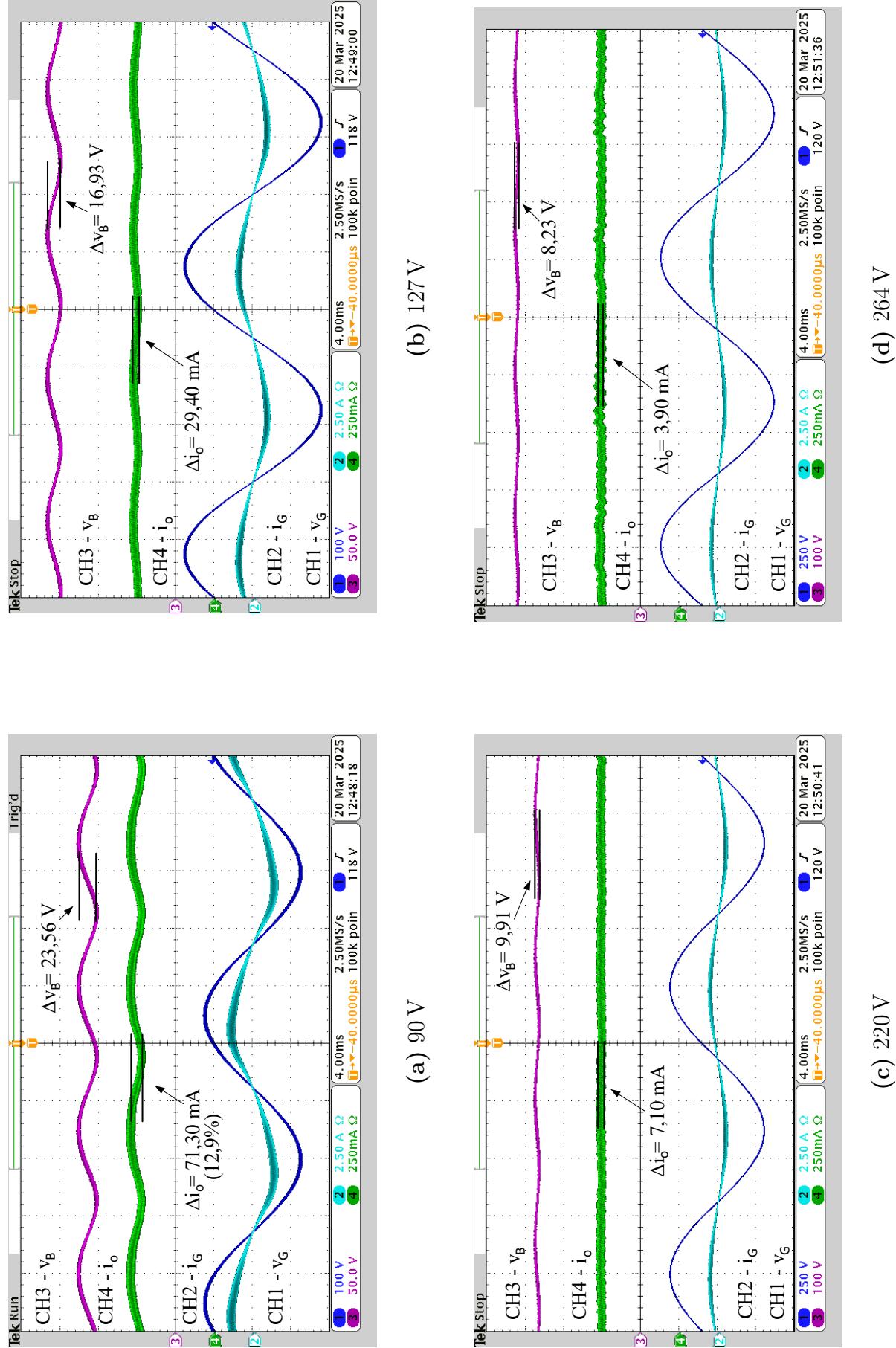

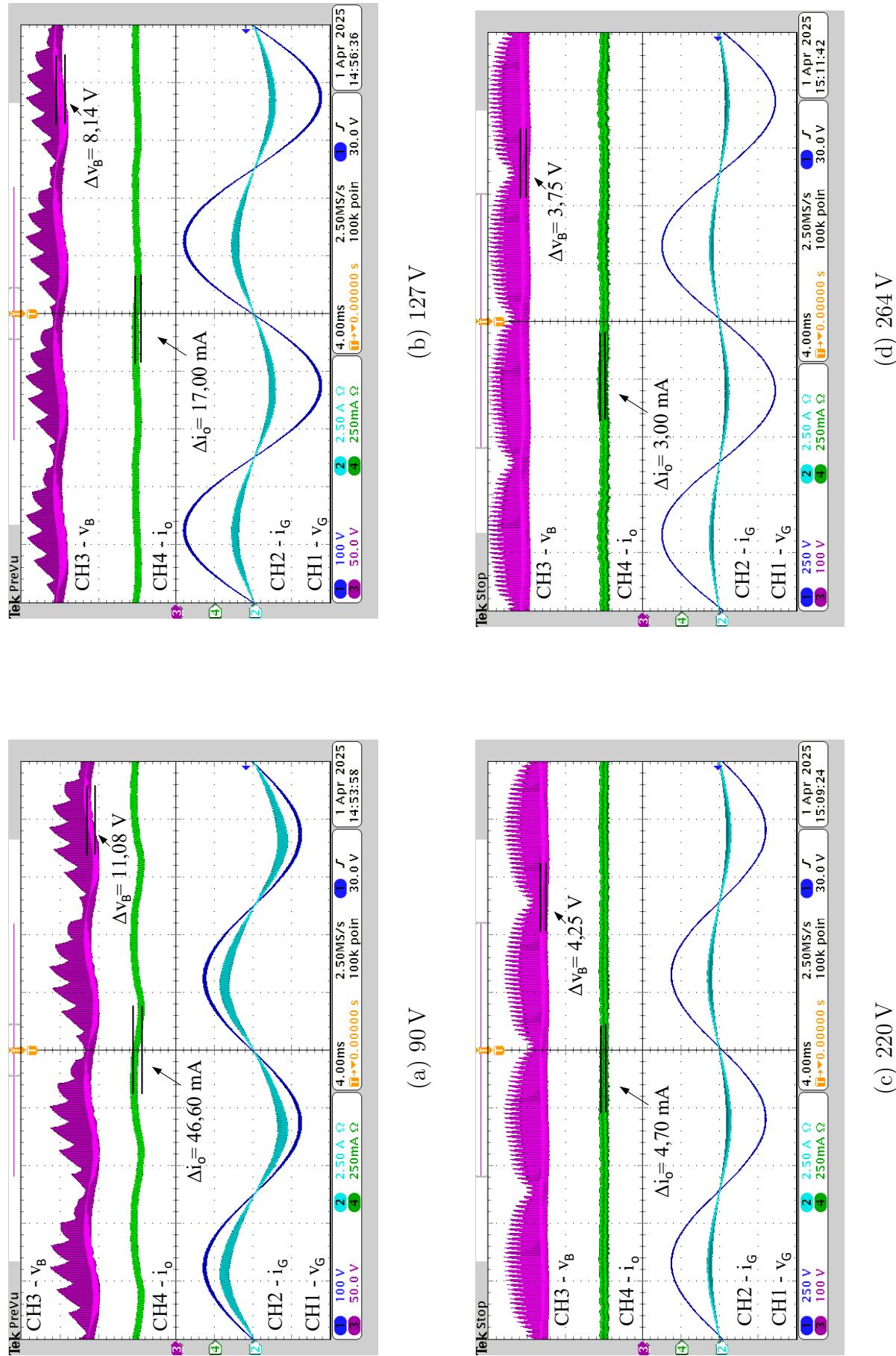

| Figura 51 | – Principais formas de onda com controle clássico em 50 Hz. . . . .                                                                                                                   | 89  |

| Figura 52 | – Capacitor em série com o reostato. . . . .                                                                                                                                          | 90  |

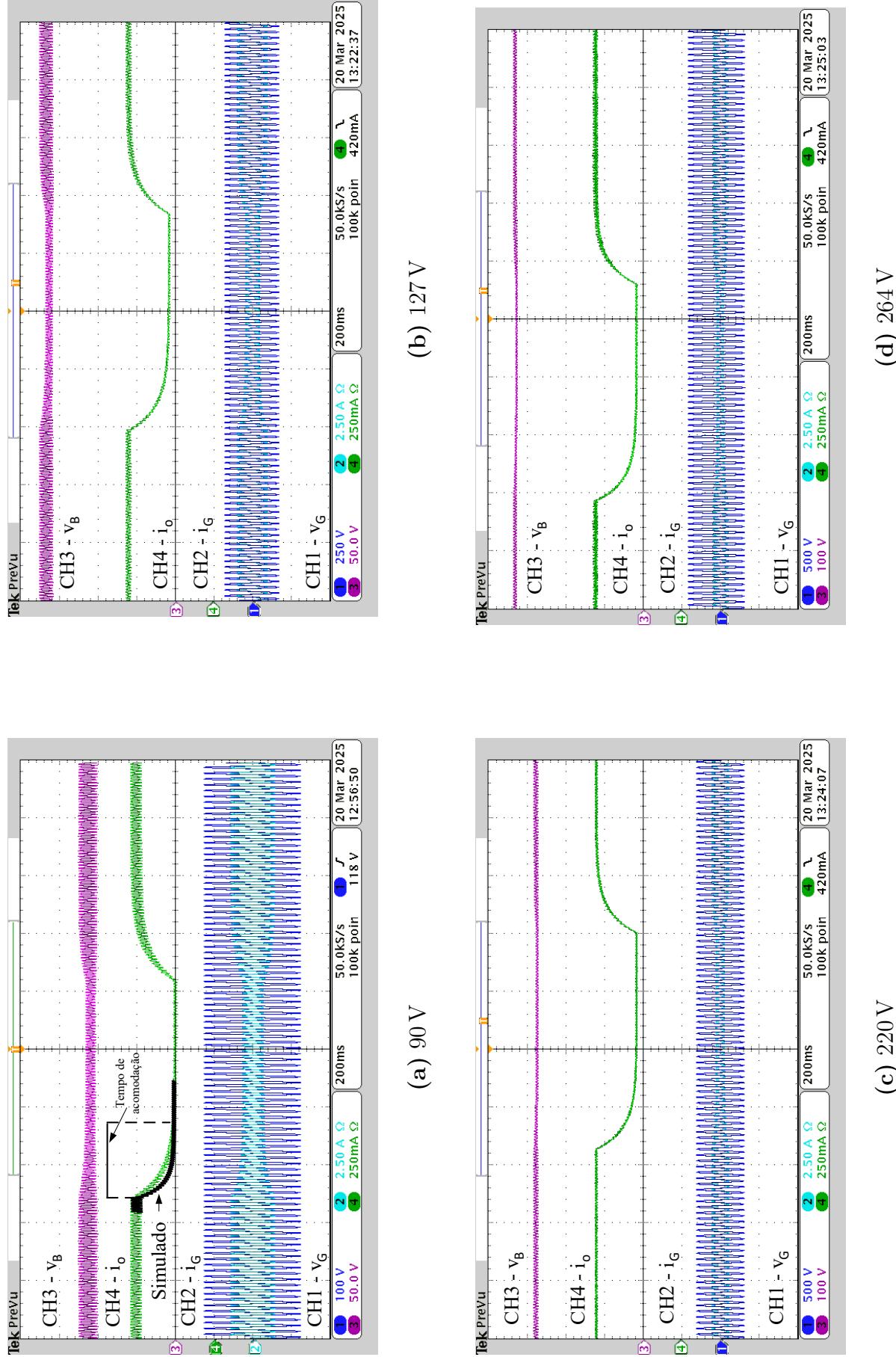

| Figura 53 | – Principais formas de onda com controle robusto em 50 Hz: (a) 90 V, (b) 127 V, (c) 220 V e (d) 264 V. . . . .                                                                        | 91  |

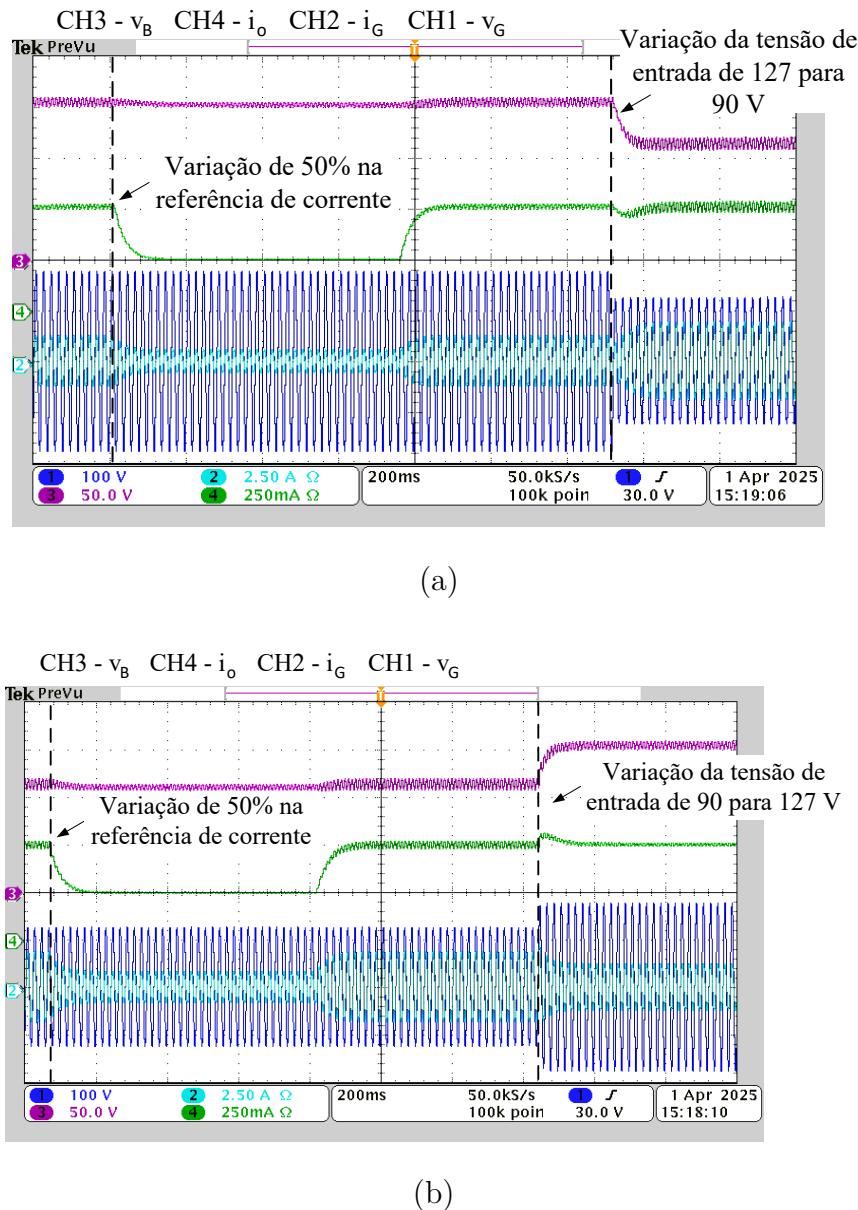

| Figura 54 | – Degrau de referência e distúrbio na tensão de entrada em 50 Hz: (a) degrau de referência, (b) distúrbio na tensão de entrada. . . . .                                               | 92  |

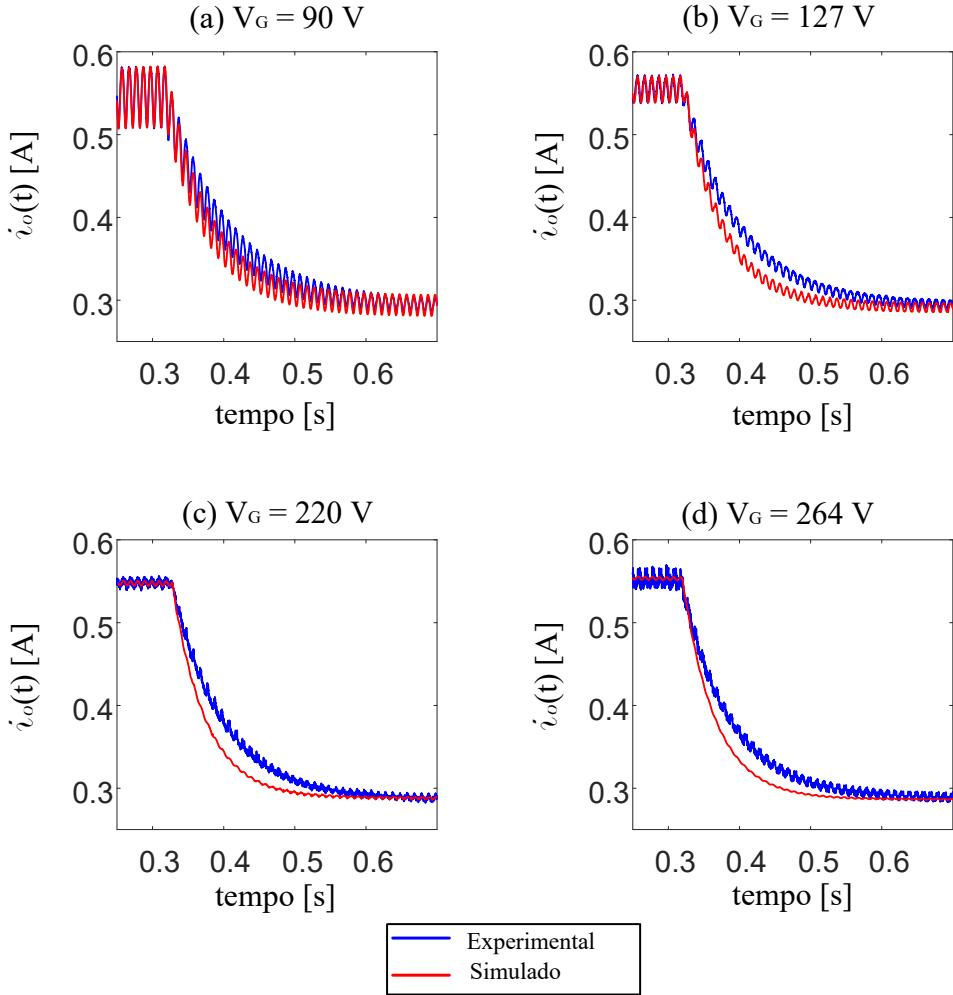

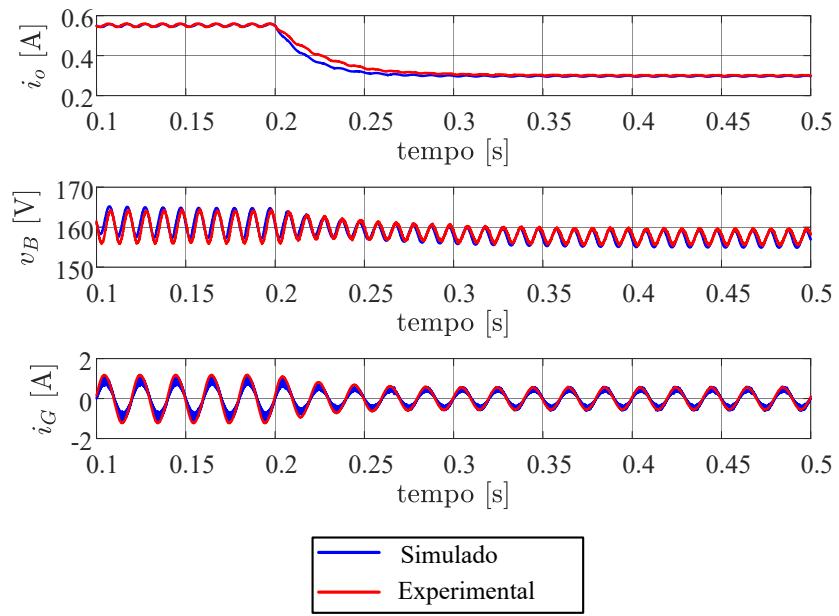

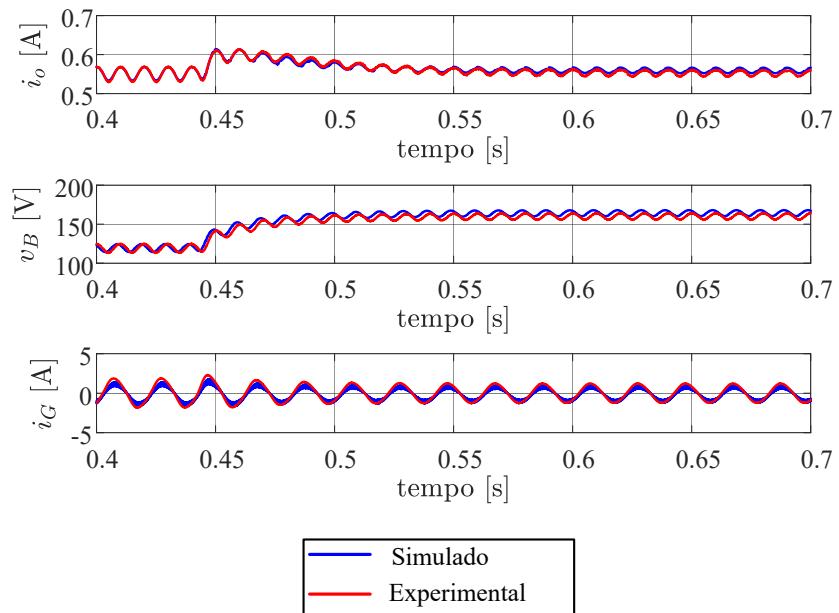

| Figura 55 | – Comparação dos resultados experimentais e de simulação com relação à variação da referência de 100% a 50% em 90 V e 50 Hz. . . . .                                                  | 93  |

| Figura 56 | – Comparação dos resultados experimentais e de simulação com relação à resposta ao distúrbio na tensão de entrada em 50 Hz. . . . .                                                   | 93  |

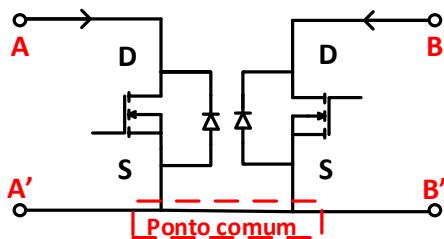

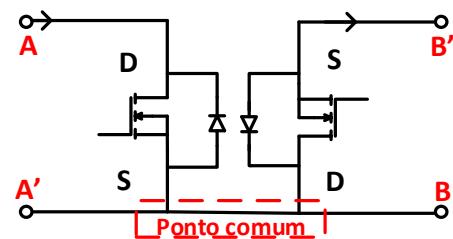

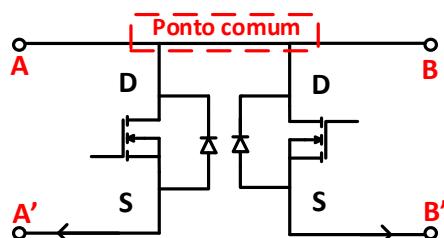

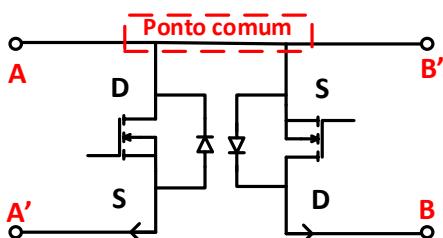

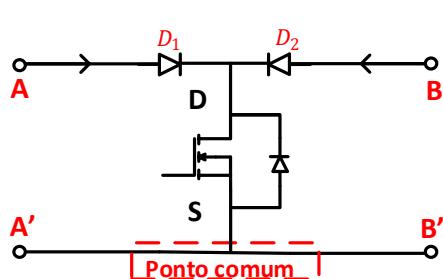

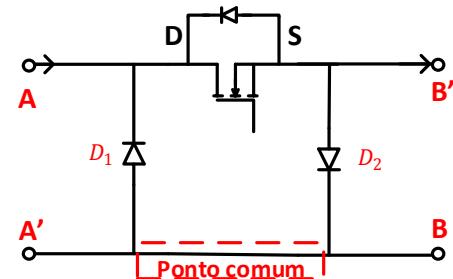

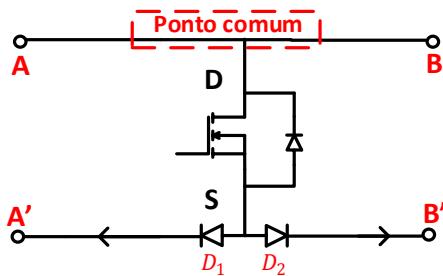

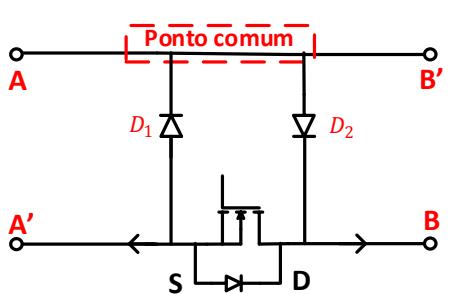

| Figura 57 | – Tipos de conexões entre dois interruptores: (a) conexão tipo T (S–S), (b) conexão tipo II (S–D), (c) conexão tipo i-T (D–D) e (d) conexão tipo i-II (D–S). . . . .                  | 105 |

| Figura 58 | – Células resultantes da integração entre dois interruptores (células de chave única): (a) conexão tipo T, (b) conexão tipo II, (c) conexão tipo i-T e (d) conexão tipo i-II. . . . . | 106 |

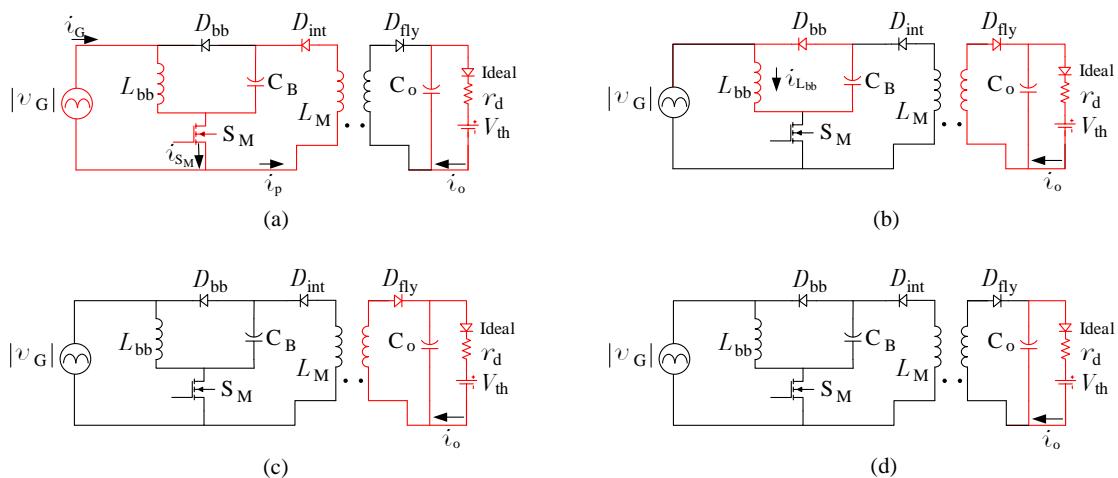

| Figura 59 | – Etapas de operação do conversor. . . . .                                                                                                                                            | 107 |

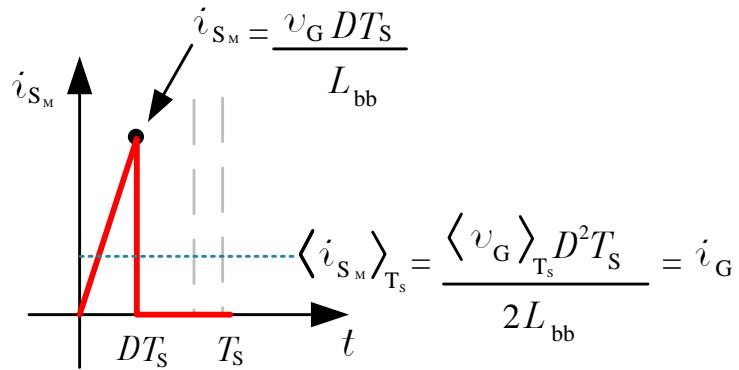

| Figura 60 | – Corrente no interruptor em um período de comutação. . . . .                                                                                                                         | 109 |

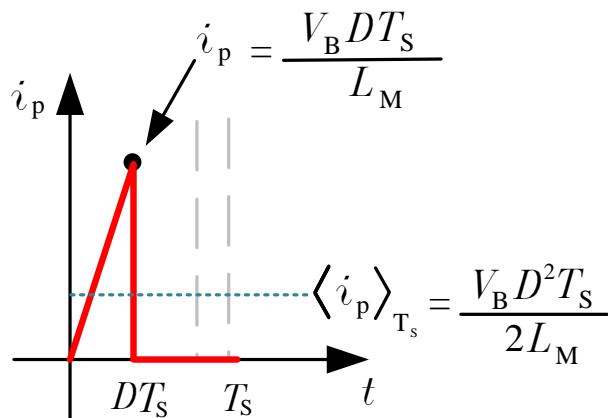

| Figura 61 | – Corrente no terminal primário do conversor <i>flyback</i> em um período de comutação. . . . .                                                                                       | 110 |

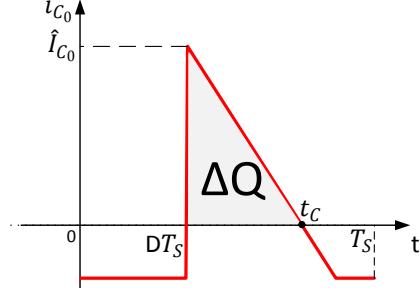

| Figura 62 | – Corrente no capacitor de saída. . . . .                                                                                                                                             | 114 |

| Figura 63 | – Região para alocação dos polos. . . . .                                                                                                                                             | 115 |

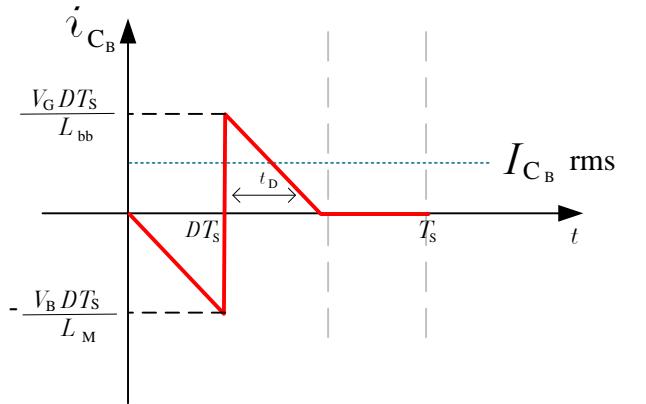

| Figura 64 | – Forma de onda da corrente de alta frequência no capacitor de barramento. . . . .                                                                                                    | 122 |

## LISTA DE TABELAS

|                                                                            |    |

|----------------------------------------------------------------------------|----|

| Tabela 1 – Limites harmônicos segundo a norma IEC - 61000-3-2 (Classe C).  | 18 |

| Tabela 2 – Parâmetros da carga LED.                                        | 44 |

| Tabela 3 – Parâmetros de entrada do sistema.                               | 46 |

| Tabela 4 – Componentes do protótipo do conversor.                          | 47 |

| Tabela 5 – Parâmetros incertos do conversor.                               | 63 |

| Tabela 6 – Desempenho dos controladores projetados.                        | 64 |

| Tabela 7 – Resultados teóricos obtidos com a técnica de controle proposta. | 65 |

| Tabela 8 – Comparaçāo do tempo de acomodação (critério de 2%)              | 76 |

| Tabela 9 – Parâmetros do modelo de degradação do capacitor.                | 81 |

## LISTA DE ABREVIATURAS E SIGLAS

|             |                                                         |

|-------------|---------------------------------------------------------|

| <b>PFC</b>  | correção do fator de potência                           |

| <b>LMIs</b> | desigualdades matriciais lineares                       |

| <b>PC</b>   | controle de potência (do inglês, <i>Power Control</i> ) |

| <b>LEDs</b> | diodos emissores de luz                                 |

| <b>PF</b>   | fator de potência                                       |

| <b>THD</b>  | distorção harmônica total                               |

| <b>ARC</b>  | compensação ativa da ondulação                          |

| <b>LFR</b>  | ondulação da componente em baixa frequência             |

| <b>ABNT</b> | Associação Brasileira de Normas Técnicas                |

| <b>IEC</b>  | International Electrotechnical Commission               |

| <b>CA</b>   | Corrente Alternada                                      |

| <b>CC</b>   | Corrente Contínua                                       |

| <b>CCM</b>  | modo de condução contínua                               |

| <b>PI</b>   | proporcional integral                                   |

| <b>PIR</b>  | proporcional integral ressonante                        |

| <b>DCM</b>  | modo de condução descontínua                            |

| <b>ESR</b>  | resistência em série equivalente                        |

| <b>ESL</b>  | indutância em série equivalente                         |

## SUMÁRIO

|          |                                                                                                         |           |

|----------|---------------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>INTRODUÇÃO . . . . .</b>                                                                             | <b>15</b> |

| 1.1      | <i>DRIVERS</i> PARA LEDs . . . . .                                                                      | 16        |

| 1.2      | FORMA DE ONDA DA CORRENTE NOS LEDs . . . . .                                                            | 17        |

| 1.3      | CAPACITORES ELETROLÍTICOS . . . . .                                                                     | 19        |

| 1.4      | MOTIVAÇÃO . . . . .                                                                                     | 22        |

| 1.5      | OBJETIVOS . . . . .                                                                                     | 22        |

| 1.6      | ESTRUTURA DA TESE . . . . .                                                                             | 23        |

| 1.7      | PUBLICAÇÕES . . . . .                                                                                   | 23        |

| <b>2</b> | <b>REVISÃO BIBLIOGRÁFICA . . . . .</b>                                                                  | <b>24</b> |

| 2.1      | TÉCNICAS DE REDUÇÃO DA CAPACITÂNCIA . . . . .                                                           | 24        |

| 2.1.1    | Topologias Alternativas para Redução da Capacitância . . . . .                                          | 24        |

| 2.1.2    | Injeção de harmônicos na corrente de entrada . . . . .                                                  | 26        |

| 2.1.3    | Compensação ativa da ondulação . . . . .                                                                | 27        |

| 2.2      | CONTROLE ROBUSTO EM <i>DRIVERS</i> DE LED . . . . .                                                     | 29        |

| 2.3      | CONCLUSÕES PARCIAIS . . . . .                                                                           | 30        |

| <b>3</b> | <b>TEORIA DE CONTROLE ROBUSTO . . . . .</b>                                                             | <b>32</b> |

| 3.1      | CONTROLE POR REALIMENTAÇÃO DE ESTADOS . . . . .                                                         | 32        |

| 3.2      | CONCEITOS BÁSICOS DE ROBUSTEZ . . . . .                                                                 | 34        |

| 3.3      | VARIAÇÕES PARAMÉTRICAS . . . . .                                                                        | 35        |

| 3.4      | ESTABILIDADE SEGUNDO LYAPUNOV . . . . .                                                                 | 37        |

| 3.5      | DESIGUALDADES MATRICIAIS LINEARES - LMIs . . . . .                                                      | 40        |

| 3.6      | ESTUDO DE CASO . . . . .                                                                                | 42        |

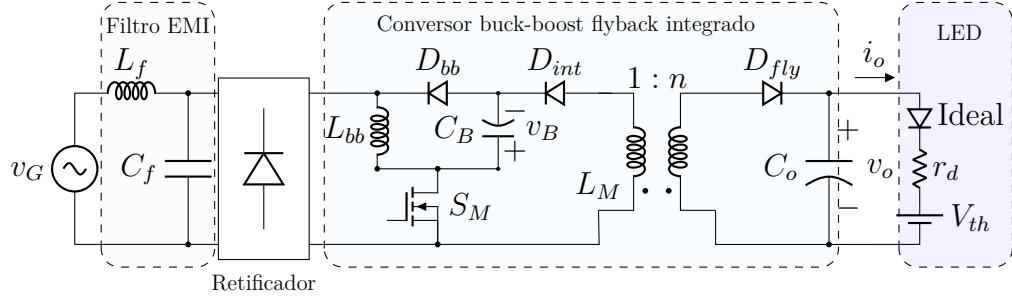

| 3.6.1    | Projeto do conversor Buck-Boost Flyback integrado . . . . .                                             | 43        |

| 3.6.2    | Modelagem dinâmica . . . . .                                                                            | 47        |

| 3.6.3    | Modelagem em espaço de estados . . . . .                                                                | 50        |

| 3.7      | CONCLUSÕES PARCIAIS . . . . .                                                                           | 50        |

| <b>4</b> | <b>APLICAÇÕES DE CONTROLE ROBUSTO EM <i>DRIVERS</i> LED . . . . .</b>                                   | <b>52</b> |

| 4.1      | MODELAGEM DA CORRENTE DE ENTRADA . . . . .                                                              | 53        |

| 4.2      | APROXIMAÇÃO TEÓRICA DA RAZÃO CÍCLICA . . . . .                                                          | 54        |

| 4.3      | COMPENSAÇÃO DA ONDULAÇÃO EM BAIXA FREQUÊNCIA NA SAÍDA DO CONVERSOR . . . . .                            | 55        |

| 4.4      | REDUÇÃO DO FILTRO CAPACITIVO . . . . .                                                                  | 57        |

| 4.4.1    | Resultados teóricos, de simulação e experimentais . . . . .                                             | 62        |

| 4.5      | APLICAÇÃO DE CONTROLE ROBUSTO PARA MITIGAR OS EFEITOS DA DEGRADAÇÃO DO CAPACITOR ELETROLÍTICO . . . . . | 77        |

| 4.5.0.1  | Resultados teóricos, de simulação e experimentais . . . . .                                             | 82        |

|          |                                                                 |            |

|----------|-----------------------------------------------------------------|------------|

| 4.6      | CONCLUSÕES PARCIAIS . . . . .                                   | 94         |

| <b>5</b> | <b>CONCLUSÕES FINAIS . . . . .</b>                              | <b>96</b>  |

| 5.1      | TRABALHOS FUTUROS . . . . .                                     | 97         |

|          | <b>REFERÊNCIAS . . . . .</b>                                    | <b>98</b>  |

|          | <b>APÊNDICE A – Método de integração de estágios de conver-</b> |            |

|          | <b>sores de potência . . . . .</b>                              | <b>105</b> |

|          | <b>APÊNDICE B – Projeto do conversor Buck-Boost Flyback</b>     |            |

|          | <b>integrado . . . . .</b>                                      | <b>107</b> |

| B.1      | Etapas de operação do conversor . . . . .                       | 107        |

| B.2      | Projeto do conversor . . . . .                                  | 108        |

| B.2.1    | Razão cíclica (D) . . . . .                                     | 108        |

| B.2.2    | Indutor do primeiro estágio . . . . .                           | 108        |

| B.2.3    | Indutância de magnetização . . . . .                            | 110        |

| B.2.4    | Ganho estático do conversor integrado . . . . .                 | 111        |

| B.2.5    | Capacitor de barramento e de saída . . . . .                    | 111        |

|          | <b>APÊNDICE C – Metodologia implementada via Matlab . . .</b>   | <b>115</b> |

|          | <b>APÊNDICE D – Potência estimada na ESR . . . . .</b>          | <b>122</b> |

## 1 INTRODUÇÃO

Os diodos emissores de luz (em inglês, *Light Emitting Diodes*, LEDs) vêm se tornando o mais popular sistema de iluminação graças às suas vantagens já bem conhecidas, tais como: (i) longa vida útil, (ii) eficiência, (iii) bom índice de reprodução de cores. Além disso, sua capacidade de dimerizar faz com que seja possível diminuir o tempo com o qual operam com máxima potência, diminuindo assim seu consumo de energia (SCHUBERT; GEESMANN; KIM, 2005; LAUBSCH *et al.*, 2009).

A implementação de LED nos sistemas de iluminação surge como uma necessidade para um desenvolvimento sustentável de uma nação. De acordo com (DREYFUS; GALLINAT, 2015), em 2015, a iluminação era responsável por 15% do consumo global de eletricidade e 5% das emissões mundiais de gases de efeito estufa. Com o aumento da população e desenvolvimento da economia, a demanda por iluminação aumenta, sendo necessário utilizar tecnologias mais eficientes.

Em função deste cenário, em 2018, é lançada a iniciativa “*United for Efficiency*” pela Organização das Nações Unidas (ONU), visando eliminar gradualmente a iluminação de baixa qualidade em países em desenvolvimento. Um dos pilares para essa transformação é o Modelo de Diretrizes, desenvolvido por parcerias públicas e privadas, com objetivo de acelerar a transição para iluminação com eficiência energética (U4E, 2018).

O Modelo de Diretrizes simplifica a implantação, adoção e aplicação da regulamentação padrão sobre eficiência de iluminação, abrangendo o escopo do produto, definições, métodos de teste e requisitos mínimos de desempenho. Além disso, países que aderirem a esse modelo poderão contar com oportunidades de compartilhamento de recursos, através da redução de barreiras comerciais (U4E, 2018).

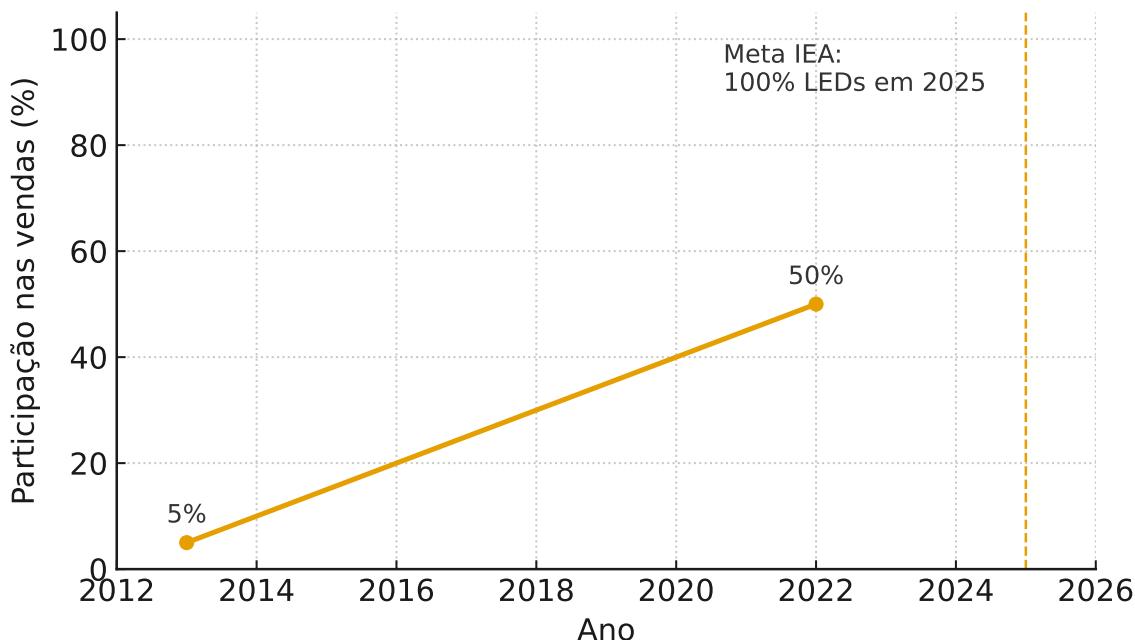

Segundo a *International Energy Agency* (IEA, 2021), a participação de LEDs nas vendas residenciais globais passou de cerca de 5% em 2013 para 50% em 2022, com tendência de alta contínua (IEA, 2023), conforme ilustrado na Figura 1. Em linha com o Cenário Net-Zero<sup>1</sup>, a própria (IEA, 2021) estabeleceu como marco a meta de 100% das vendas de iluminação em LED até 2025 (IEA, 2022).

---

<sup>1</sup> Cenário Net-Zero: Compromisso entre indivíduos, empresas e governos para compensar as emissões de gases de efeito estufa na atmosfera até 2030.

Figura 1 – Participação de LEDs nas vendas globais de iluminação (pontos selecionados) e marco NZE da IEA (100% de vendas em LED até 2025).

Fonte: Elaborado pelo autor (2025), com dados de (IEA, 2023; IEA, 2022).

A mudança para iluminação LED é uma das maneiras mais rápidas e baratas de proporcionar economia de energia e de carbono.

“As lâmpadas são o fruto mais barato da árvore da eficiência. Nenhum outro produto oferece economias tão atraentes por produto. Os LEDs consomem até 90% menos energia do que as lâmpadas incandescentes convencionais” (Noah Horowitz, diretor do Centro de Padrões de Eficiência Energética do Conselho de Defesa dos Recursos Naturais) (IEA, 2021).

Em síntese, a iluminação baseada em LEDs é hoje um vetor central para metas de eficiência energética e descarbonização, oferecendo alta eficácia luminosa, longa vida útil e ampla integração com controle e dimerização inteligentes.

### 1.1 *DRIVERS PARA LEDs*

Uma característica das cargas de iluminação a LED é que elas operam em baixas tensões e em corrente contínua, impossibilitando a conexão direta com a rede elétrica convencional. Além da necessidade de um retificador, responsável por realizar a conversão Corrente Alternada (CA)/Corrente Contínua (CC) para a carga, um dispositivo eletrônico é utilizado para manter a corrente e tensão fornecida ao LED dentro dos parâmetros indicados para sua operação. Geralmente, este dispositivo eletrônico é um conversor estático de

potência, que deve atender requisitos mínimos de qualidade de energia consumida, tais como: alto fator de potência (em inglês, *Power Factor*, PF) e baixa distorção harmônica total (em inglês, *Total Harmonic Distortion*, THD) na corrente de entrada.

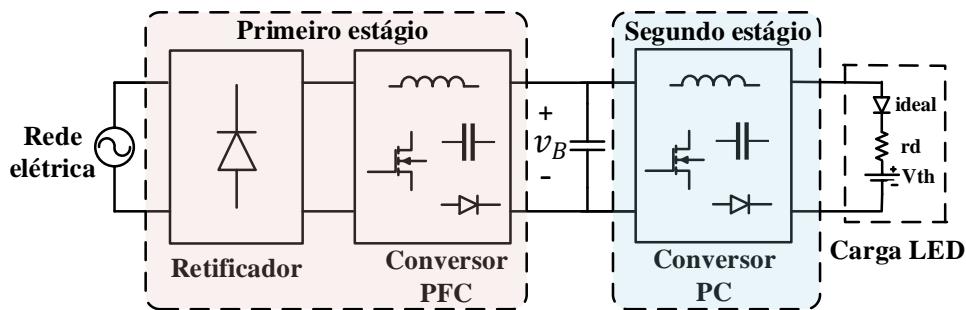

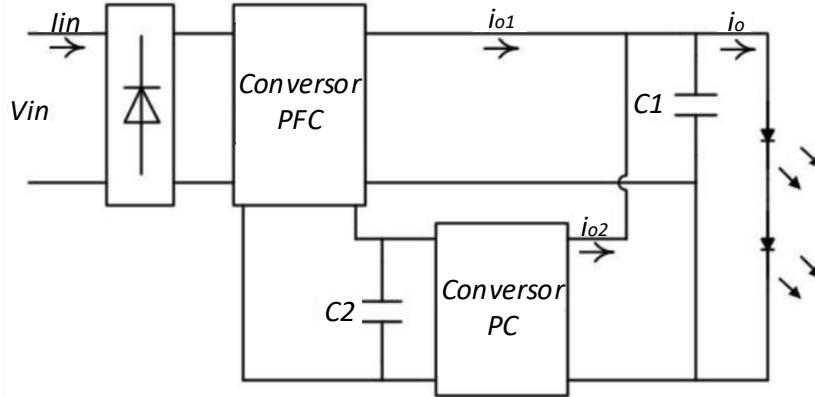

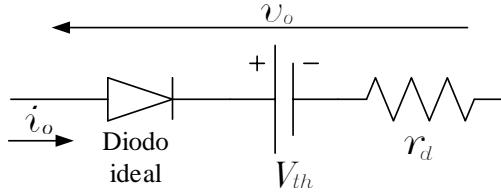

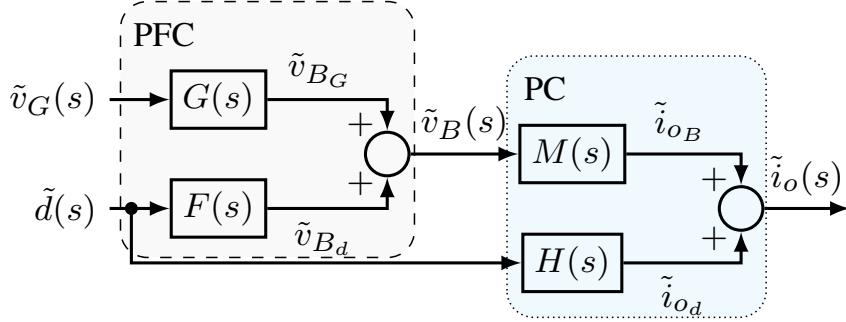

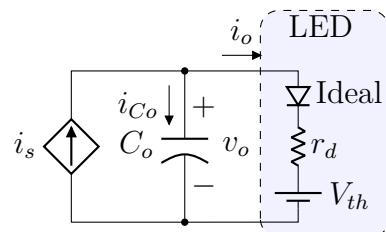

Na literatura, estes dispositivos são conhecidos como “*drivers*” (ALONSO *et al.*, 2011; BRITTO *et al.*, 2008; BARDSLEY *et al.*, 2013; HUI *et al.*, 2010), na Figura 2 é ilustrada a configuração de um *driver* de dois estágios em cascata. O primeiro estágio é composto por um retificador e um conversor estático de potência, responsável pela correção do fator de potência (PFC). O segundo estágio, denominado de estágio de controle de potência (do inglês, *Power Control*) (PC), tem o objetivo de estabilizar a corrente nos LEDs. A carga é modelada por um diodo ideal, uma fonte de tensão ideal com polaridade contrária ao sentido da corrente, representando sua tensão de limiar ( $V_{th}$ ) e uma resistência série ( $r_d$ ) (SCHUBERT, 2018).

Figura 2 – *Driver* de dois estágios.

Fonte: Elaborado pelo autor (2025).

O fator de potência no qual o *driver* deve operar, segundo a Associação Brasileira de Normas Técnicas (ABNT) (ABNT, 2012) de dispositivos eletrônicos para módulos de LED, deve ser superior a 0,92. Além disso, o conteúdo harmônico injetado na rede deve estar de acordo com as normas da International Electrotechnical Commission (IEC), especificamente segundo a norma IEC - 61000-3-2 classe C (IEC, 2014), que se refere aos sistemas de iluminação com potência ativa acima de 25 W. Os limites de conteúdo harmônico exigidos segundo a norma são indicados na Tabela 1.

\*fp = fator de potência.

## 1.2 FORMA DE ONDA DA CORRENTE NOS LEDs

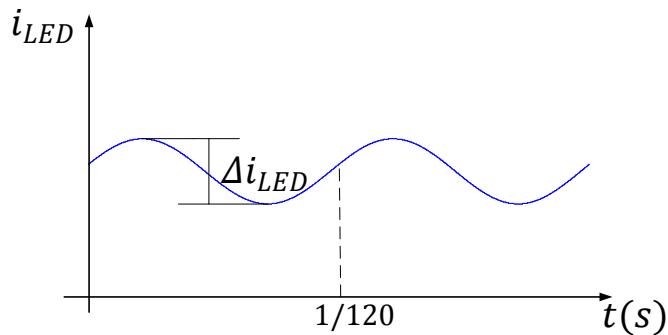

A forma de onda entregue à carga, para uma rede de alimentação com frequência de 60 Hz, será composta por um valor CC com ondulação, CA, na frequência de 120 Hz ( $\Delta i_{LED}$ ), como é ilustrado na Figura 3.

Tabela 1 – Limites harmônicos segundo a norma IEC - 61000-3-2 (Classe C).

| Ordem harmônica<br>(h) | Corrente máxima permitida<br>(em % com relação à fundamental) |

|------------------------|---------------------------------------------------------------|

| 2                      | 2 %                                                           |

| 3                      | 0,3fp                                                         |

| 5                      | 10 %                                                          |

| 7                      | 7 %                                                           |

| 9                      | 5 %                                                           |

| $11 < h < 39$          | 3 %                                                           |

Fonte: Adaptado da IEC 61000-3-2 (Classe C).

Figura 3 – Forma de onda da corrente no LED.

Fonte: Adaptado de (SOARES, 2017).

A ondulação da componente em baixa frequência (em inglês, *Low Frequency Ripple*, LFR) da forma de onda da corrente no LED ocasiona uma oscilação na iluminância, denominado de *flicker*, que por sua vez leva a um efeito prejudicial ao ser humano, desencadeando dores de cabeça, enxaquecas e até mesmo convulsões epilépticas. Em (IEEE, 2015), é quantificada a relação da ondulação da corrente na carga LED com os riscos à saúde provocados pelo *flicker*, sendo que esta relação pode ser correlacionada com a frequência da onda ( $f_{flicker}$ ) da seguinte maneira:

- Condição de baixo risco:  $\Delta i_{LED} \leq 0,16 f_{flicker}$  - atenua qualquer distração ou efeito biológico negativo causado pelo *flicker*;

- Efeito não-observável:  $\Delta i_{LED} \leq 0,066 f_{flicker}$ .

Portanto, em alguns países, onde a rede de alimentação possui frequência de 60 Hz, o valor máximo do LFR, para efeito de baixo risco ao ser humano, deve ser de  $0,19 I_o$ . Já em países europeus, onde geralmente a rede de alimentação possui frequência de 50 Hz, o valor máximo é de  $0,16 I_o$ .

A filtragem da ondulação em baixa frequência, em um *driver* de dois estágios, é realizada pelo capacitor de barramento, e para manter em certo limite é necessário um capacitor de elevada capacidade, geralmente pelo empregado de capacitores eletrolíticos.

### 1.3 CAPACITORES ELETROLÍTICOS

Os capacitores eletrolíticos constituem o elo mais fraco dos *drivers*, são os principais responsáveis pela diminuição da confiabilidade e vida útil do sistema. De acordo com (ZHOU *et al.*, 2012), 50% da taxa de falhas em conversores eletrônicos de potência são relacionadas ao mau funcionamento de capacitores eletrolíticos.

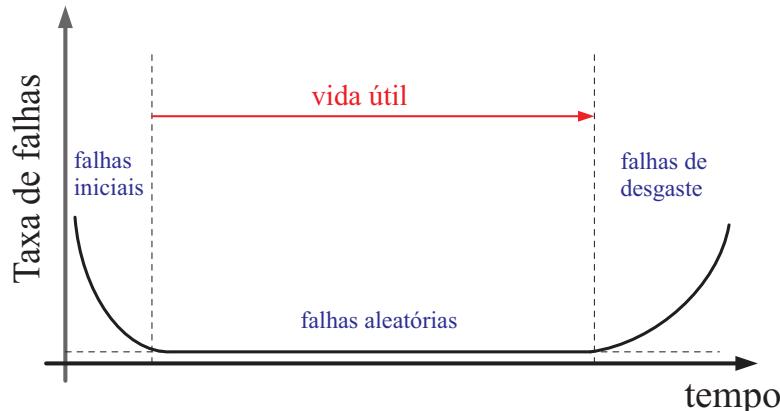

Dentre as principais falhas deste componente, podemos citar: (i) falhas relacionadas ao processo de fabricação do componente, denominadas falha iniciais; (ii) falhas relacionadas a eventos inesperados, também conhecidas como falhas aleatórias, ocorrendo durante a vida útil do componente e (iii) falhas que ocorrem devido à degradação natural, denominadas falhas de desgaste (SOARES, 2017). A Figura 4 mostra o comportamento das taxas de falhas dos capacitores ao longo do tempo.

Figura 4 – Taxa de falhas em capacitores ao longo do tempo.

Fonte: Adaptado de (SOARES, 2017).

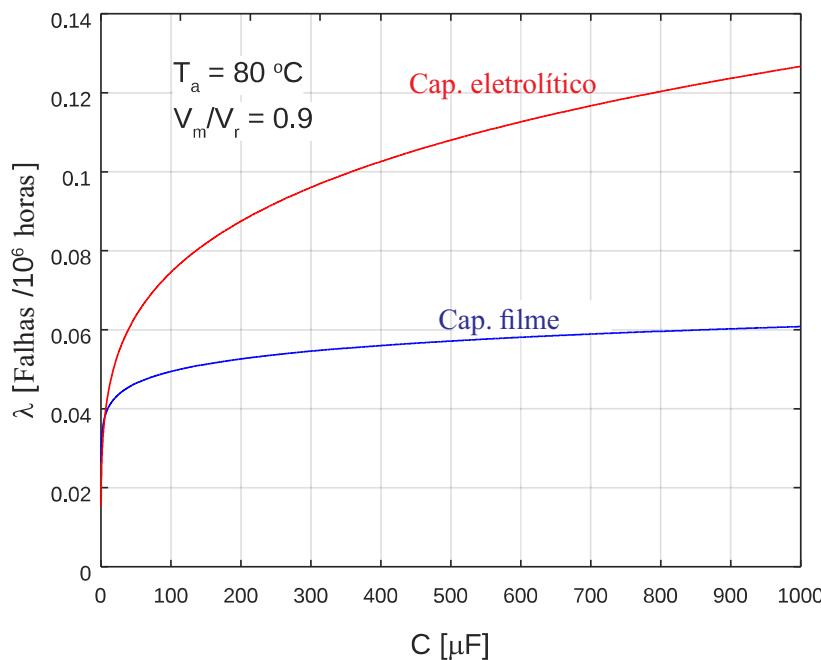

Em (SOARES, 2017), é analisada a taxa de falha em função da capacidade para capacitores eletrolíticos e de filme, com base no modelo apresentado em (HARMS, 2010). Na Figura 5, é ilustrado o número de falhas em função do tempo  $\lambda$ , de acordo com a capacidade, considerando uma temperatura ambiente de 80 °C e uma tensão de pico no capacitor ( $V_m$ ) equivalente à 90% da máxima tensão permitida para o componente ( $V_r$ ).

Há duas alternativas para diminuir a taxa de falha deste componente e, consequentemente, aumentar a confiabilidade e vida útil. A primeira alternativa consiste na substituição de capacitores eletrolíticos por capacitores de filmes, pois estes apresentam uma menor taxa de falhas para uma grande faixa de valores de capacidade. No entanto, os capacitores também devem ser analisados com relação à densidade de potência, pois,

Figura 5 – Taxa de falhas em função da capacitância.

Fonte: Adaptado de (SOARES, 2017).

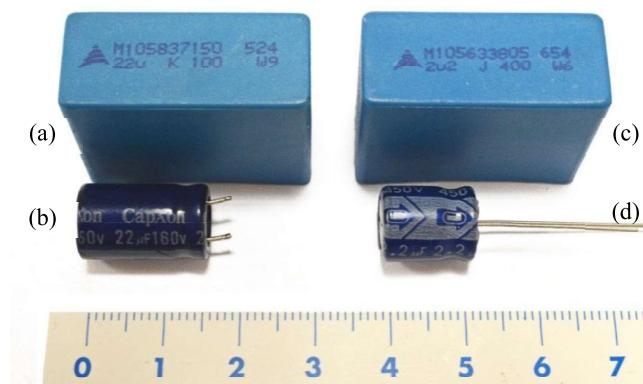

Figura 6 – Comparação entre volume e densidade de carga de capacitores de filme e eletrolíticos. (a) Capacitor de filme de 22  $\mu\text{F}$  e 100 V – 10,5 cm<sup>3</sup>. (b) Capacitor eletrolítico de 22  $\mu\text{F}$  e 160 V – 5,3 cm<sup>3</sup>. (c) Capacitor de filme de 2,2  $\mu\text{F}$  e 400 V – 10,5 cm<sup>3</sup>. (d) Capacitor eletrolítico de 2,2  $\mu\text{F}$  e 450 V – 4,1 cm<sup>3</sup>. Régua em centímetros.

Fonte: Adaptado de (ALMEIDA, 2014).

em algumas situações, o espaço disponível para o dispositivo eletrônico é limitado no sistema de iluminação. A segunda alternativa é a utilização de capacitores eletrolíticos de baixa capacitância, uma vez que a diminuição da capacitância também produz uma diminuição na taxa de falhas do componente, como se conclui da Figura 5.

Em (ALMEIDA, 2014), é realizada uma comparação entre a densidade de potência de capacitores eletrolíticos e de filme, como mostrado na Figura 6. É possível notar que a densidade de potência de capacitores eletrolíticos seja de 4 a 5 vezes maior que as de filme, apresentando menor volume para as mesmas capacitâncias e tensões similares. Portanto, a segunda alternativa fornece ao *driver* uma maior confiabilidade e densidade de potência.

Além disso, os capacitores eletrolíticos são identificados como o ponto mais vulnerável nos sistemas de iluminação LED, especialmente quando comparados à sua vida útil (LALL; SAKALAUKUS; DAVIS, 2015). A expectativa de vida da carga LED varia de 25 000 a 100 000 h (QIAN *et al.*, 2016). Notavelmente, os capacitores eletrolíticos empregados nos *drivers* LED não apresentam uma durabilidade correspondente à dos LEDs.

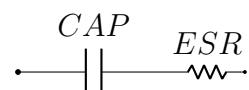

O capacitor eletrolítico é conceitualmente modelado como um capacitor ideal (CAP) conectado com uma resistência em série equivalente (em inglês, *Equivalent Series Resistance*, ESR), conforme ilustrado na Figura 7. Embora seja possível incluir uma indutância em série equivalente (em inglês, *Equivalent Series Inductance*, ESL) neste modelo, para a maioria dos *drivers* de LED convencionais, o valor da ESL é consideravelmente baixo e, portanto, pode ser desprezado (CHEN *et al.*, 2008).

Figura 7 – Circuito equivalente do capacitor eletrolítico.

Fonte: Elaborado pelo autor (2025).

A performance dos capacitores eletrolíticos é impactada por uma combinação de fatores elétricos, térmicos, mecânicos e ambientais. Durante o processo de degradação do componente, a evaporação do líquido contido no capacitor acelera devido ao aumento da temperatura operacional e à ondulação de corrente, culminando no aumento da ESR e na redução da capacitância (ABDENNADHER *et al.*, 2010).

Autores como (VENET; DARNAND; GRELLET, 1993; KÖTZ; RUCH; CERICOLA, 2010) consideraram uma falha no capacitor quando há um aumento que corresponde ao dobro do valor inicial da ESR e uma diminuição de 20% na capacitância. Diversas pesquisas têm investigado a degradação dos capacitores, propondo modelos para antecipar falhas (SUN *et al.*, 2016; SUN *et al.*, 2015). O processo de degradação do capacitor resulta em um aumento na ondulação de saída, podendo provocar falhas na regulação da ondulação de saída do conversor ou, em casos extremos, danificar o próprio conversor.

## 1.4 MOTIVAÇÃO

Com base nas seções anteriores, esse trabalho possui como foco apresentar aplicações de controle robusto em *drivers* LED, visando assegurar uma maior vida útil e confiabilidade ao sistema, ao mesmo tempo em que atende aos requisitos mínimos de qualidade de energia e redução da ondulação de baixa frequência na corrente dos LEDs. Prevendo a construção de um protótipo a ser conectado em redes ca típicas, o *driver* é projetado para operar dentro de uma faixa de tensão eficaz de 90 a 264 V, fornecendo uma corrente constante em uma faixa de potências, o que permite a conexão de diferentes arranjos de LEDs, incluindo a possibilidade de dimerização, que proporcionará uma maior eficiência energética ao sistema elétrico.

Devido à variação da tensão de entrada, o modelo dinâmico do sistema, utilizado para fins de modelagem e controle, não é fixo, mas sim uma função do ponto de operação atual. Tradicionalmente, os sistemas de controle são projetados para um único ponto de operação. No entanto, essa abordagem não garante a estabilidade do sistema nem uma resposta transitória satisfatória para todos os pontos de operação (OLALLA *et al.*, 2008). Portanto, para contornar os problemas mencionados anteriormente, é adotada uma técnica de controle robusto (ZHOU; DOYLE; GLOVER, 1996; SKOGESTAD; POSTLETHWAITE, 2005) baseada em realimentação completa de estados. Uma resposta transitória satisfatória é alcançada ao alocar os polos dentro de uma região pré-definida no plano complexo para qualquer ponto de operação. O vetor de ganhos da realimentação de estados é determinado por meio de desigualdades matriciais lineares (em inglês, *Linear Matrix Inequalities*, LMIs) (DUAN; YU, 2013). A técnica de otimização  $\mathcal{H}_\infty$  (FRANCIS, 1987) é empregada em uma metodologia para reduzir o filtro capacitivo utilizado no driver, o que diminui a taxa de falhas do componente, aumentando assim sua confiabilidade. Em outra aplicação, a otimização  $\mathcal{H}_\infty$  é utilizada para manter os requisitos mínimos de qualidade de energia e redução da ondulação na saída ao longo do período de degradação do capacitor eletrolítico, aumentando assim a vida útil do *driver*.

## 1.5 OBJETIVOS

Para alcançar o objetivo deste trabalho, os seguintes tópicos serão abordados:

1. Desenvolver uma metodologia utilizando a otimização  $\mathcal{H}_\infty$  por meio de LMIs para reduzir o filtro capacitivo em *drivers* de LEDs, sem comprometer os requisitos mínimos de qualidade de energia, visando aumentar a confiabilidade do sistema.

2. Aplicar a otimização  $\mathcal{H}_\infty$  através de LMIs para manter o desempenho do *driver* diante da degradação do capacitor eletrolítico ao longo do tempo, com o intuito de prolongar a vida útil do sistema.

3. Implementar a técnica proposta em um *driver* de LEDs universal.

4. Validar os estudos teóricos por meio de resultados de simulação e experimentação.

## 1.6 ESTRUTURA DA TESE

No Capítulo 2 são apresentadas as principais técnicas encontradas na literatura para a redução da capacidade em *drivers* de LED, bem como os trabalhos mais relevantes que exploram a aplicação de métodos de controle moderno nesses sistemas.

O Capítulo 3 discute os conceitos fundamentais de controle robusto, com ênfase nas desigualdades matriciais lineares (LMIs), destacando suas vantagens e aplicações. Nesse capítulo também é desenvolvido um estudo de caso com o *driver* utilizado neste trabalho, abrangendo sua modelagem estática e dinâmica, de forma a fornecer a base necessária para o projeto do controle robusto.

No Capítulo 4 são apresentadas as aplicações de controle robusto propostas para *drivers* de LED. São descritos os procedimentos de projeto e mostrados os resultados teóricos, de simulação e experimentais que validam a metodologia desenvolvida.

Por fim, o Capítulo 5 reúne as conclusões gerais do trabalho, destacando as contribuições alcançadas e sugerindo possíveis direções para pesquisas futuras.

## 1.7 PUBLICAÇÕES

- SILVA, Bruno H. da et al. Universal-input integrated LED driver with robust  $\mathcal{H}_\infty$  controller for full-range high power factor and dimming capabilities under low current ripple. Electrical Engineering, v. 105, n. 3, p. 1897-1910, 2023.

## 2 REVISÃO BIBLIOGRÁFICA

Quando se aborda a pesquisa em *drivers* de LED, o principal desafio enfrentado está relacionado ao capacitor eletrolítico. Conforme discutido anteriormente, a utilização de capacitores eletrolíticos de baixa capacidade resulta em uma redução significativa na taxa de falhas do componente, o que, por sua vez, aumenta a confiabilidade do sistema. Além disso, estratégias de redução de capacidade podem ser empregadas para lidar com a degradação do capacitor eletrolítico, uma vez que envolvem o uso de capacitores com valores reduzidos, mantendo ainda a conformidade com os requisitos de qualidade de energia no *driver*, proporcionando assim maior vida útil ao sistema. Portanto, neste capítulo, serão destacadas as principais técnicas encontradas na literatura voltadas para a redução da capacidade em *drivers* de LEDs e aplicações de controle moderno nesses sistemas.

### 2.1 TÉCNICAS DE REDUÇÃO DA CAPACITÂNCIA

A utilização de capacitores eletrolíticos, com elevados valores de capacidade diminui a confiabilidade do sistema. Para solucionar esse problema, diferentes trabalhos buscam a redução do valor do filtro capacitivo em conversores aplicados no acionamento de LEDs.

Dentre as soluções propostas para alcançar esse objetivo, três técnicas destacam-se na literatura (LUZ *et al.*, 2017): (i) topologias alternativas de conversores para redução da capacidade, (ii) injeção de harmônicos na corrente de entrada e (iii) através da ação do controlador, também conhecido como compensação ativa da ondulação (ARC).

#### 2.1.1 Topologias Alternativas para Redução da Capacitância

Algumas formas de reduzir o valor da capacidade utilizado nos *drivers* se baseiam em alterações topológicas nos conversores eletrônicos de potência. Desse modo, a filtragem da ondulação em baixa frequência na saída é realizada por um sistema eletrônico, permitindo a redução da capacidade responsável por essa tarefa.

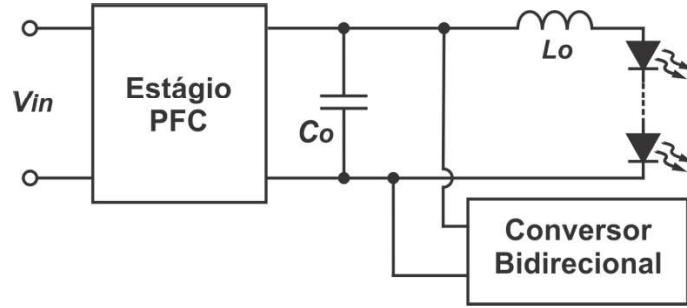

Soluções apresentadas em (REDDY; NARASIMHARAJU, 2017; HE; RUAN; ZHANG, 2017; WANG *et al.*, 2012) utilizam um conversor estático bidirecional em paralelo com o capacitor de barramento, de modo que o auxilie na tarefa de filtragem da ondulação em baixa frequência. Através dessa proposta, os autores conseguiram uma redução do valor do LFR em torno de 90%. A estrutura simplificada de uma dessas soluções é ilustrada na Figura 8.

Em (CAMPONOGARA *et al.*, 2015; VALIPOUR; REZAZADEH; ZOLGHADRI, 2015), os autores propõem a conexão entre os estágios de potência do *driver* de forma

Figura 8 – Compensação da ondulação através de um conversor bidirecional.

Fonte: Adaptado de (HE; RUAN; ZHANG, 2017).

otimizada. O estágio PFC processa apenas o nível CC da potência, enquanto a conexão PFC + PC é responsável pela ondulação de baixa frequência. Com essa estrutura, foi possível reduzir o valor do filtro capacitivo no sistema. A conexão entre os estágios do conversor, de acordo com umas dessas soluções, é mostrada na Figura 9.

Figura 9 – Conexão entre os estágios de potência de forma otimizada.

Fonte: Adaptado de (VALIPOUR; REZAZADEH; ZOLGHADRI, 2015).

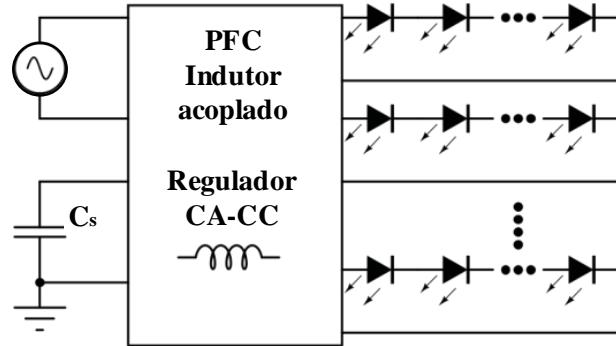

A solução proposta por (WU *et al.*, 2019) utiliza um indutor acoplado de enrolamento duplo com função PFC para cada arranjo de LEDs e uma pequena capacitância de armazenamento para desacoplar as potências de entrada CA e CC. Com este método, os autores conseguiram reduzir o valor da capacitância de tal forma que tornasse possível a utilização de capacitores de filme. O sistema proposto é ilustrado na Figura 10.

Uma desvantagem da estrutura de potência modificada é o aumento do número de componentes e circuitos de acionamento, aumentando a complexidade do sistema e reduzindo sua confiabilidade.

Figura 10 – PFC com indutor acoplado e regulador CA-CC.

Fonte: Adaptado de (WU *et al.*, 2019).

### 2.1.2 Injeção de harmônicos na corrente de entrada

Considerando um fator de potência unitário, devido ao estágio de correção do fator de potência (PFC), a potência instantânea de entrada do *driver* de LEDs pode ser expressa em função da tensão e da corrente da rede elétrica.

Denotando por  $v_G(t)$  a tensão instantânea de entrada (tensão da rede) e por  $i_G(t)$  a corrente instantânea de entrada do conversor, tem-se:

$$p_G(t) = v_G(t) i_G(t) = \sqrt{2}V_G \sin(\omega_L t) \sqrt{2}I_G \sin(\omega_L t) = V_G I_G - V_G I_G \cos(2\omega_L t), \quad (2.1)$$

em que  $V_G$  e  $I_G$  representam, respectivamente, os valores eficazes da tensão e da corrente de entrada, e  $\omega_L$  é a frequência angular da rede.

onde  $\omega_L$  é a frequência angular da linha, ao passo que  $V_G$  e  $I_G$  são os valores eficaz da tensão e corrente, suposto tensão e corrente senoidais, respectivamente.

Através da equação (2.1), é possível observar que a potência de entrada é composta por uma parcela CC e uma parcela CA. A técnica proposta tem o objetivo de diminuir a parcela CA, responsável pelo LFR na carga LED. Desta forma, a potência instantânea de entrada não possui tanta disparidade em comparação com a potência de saída do conversor. Devido a essa menor diferença entre os valores instantâneos de potência, é possível reduzir o valor do filtro capacitivo empregado na filtragem da ondulação em baixa frequência. Isso é feito inserindo harmônicas na corrente de entrada através do controle da corrente de entrada, onde a referência não é uma senoide na frequência angular da rede, mas sim acrescida de harmônicas.

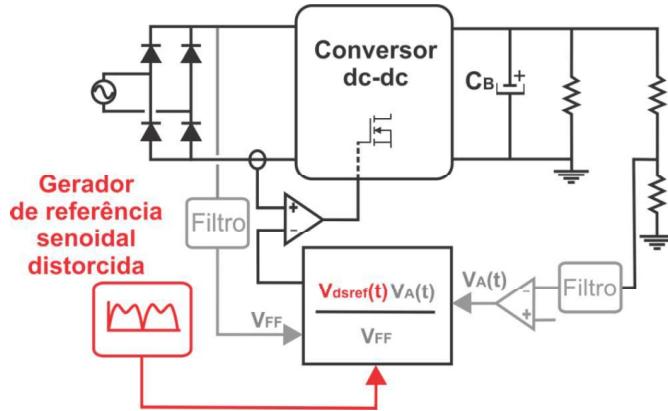

Em (LAMAR *et al.*, 2012), é utilizada uma malha de controle da corrente de entrada distorcida até o limite da norma IEC - 61000-3-2 classe C (IEC, 2014). Os autores

conseguiram diminuir a parcela CA da potência de entrada de tal forma que foi possível uma redução de até 50% no valor da capacitância de barramento, destinado à filtragem do LFR. Na Figura 11 é representado o circuito de controle utilizado nesta metodologia, onde é possível notar que duas malhas de controle são necessárias para a aplicação deste método.

Figura 11 – Controle da corrente de entrada distorcida.

Fonte: Adaptado de (LAMAR *et al.*, 2012).

Em (GU *et al.*, 2009), a referência de corrente rastreada é uma senoide acrescida da 3<sup>a</sup> harmônica. Com essa técnica, os autores conseguiram realizar a redução do valor da capacitância para 65% do valor nominal. Uma estratégia similar foi realizada em (WONG *et al.*, 2016), e o acréscimo da 5<sup>a</sup> harmônica na referência de corrente de entrada foi feita em (WANG *et al.*, 2010).

Os trabalhos que utilizam essa abordagem mostram ser possível reduzir o LFR através da redução da parcela CA da potência de entrada com a inserção de harmônicos na corrente de entrada. Uma desvantagem dessa técnica é a complexidade de controle, pois há a necessidade de duas malhas. Uma malha é utilizada para a referência senoidal da corrente de entrada acrescida de harmônicas, enquanto a outra garante o valor médio da corrente de saída.

### 2.1.3 Compensação ativa da ondulação

Outra maneira de propiciar a redução do valor do filtro capacitivo em sistemas de acionamentos de LEDs é através da ação de controle, também conhecida como compensação ativa da ondulação (em inglês, *Active Ripple Compensation*, ARC). Neste método, o controlador atua na redução da ondulação de baixa frequência na corrente dos LEDs, assim, é possível reduzir o valor da capacitância necessária para manter a ondulação no nível desejável.

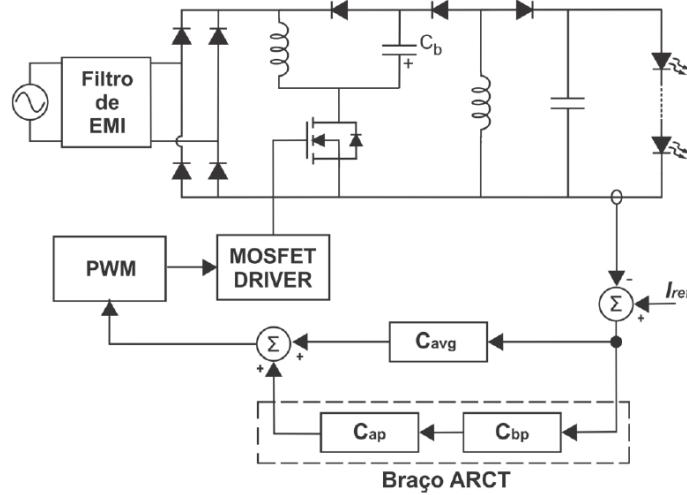

Os trabalhos apresentados em (SOARES *et al.*, 2017; SOARES; ALONSO; BRAGA, 2018) propõem que o sinal de controle seja gerado por dois ramos desacoplados em frequência. O ramo Cavg é responsável pela geração do valor médio e o Braço ARCT é responsável por gerar a parte CA do sinal. Em (SOARES *et al.*, 2017), os autores conseguiram uma redução de 46% do valor nominal da capacitância. Essa técnica de controle é ilustrada na Figura 12.

Figura 12 – Compensação ativa da ondulação.

Fonte: Adaptado de (SOARES *et al.*, 2017).

Em (COSETIN *et al.*, 2014; SOARES *et al.*, 2018) é demonstrada uma técnica de redução de capacitância através da aplicação do controlador proporcional integral (PI). O compensador PI é projetado para atuar na frequência de ondulação da corrente nos LEDs, ou seja, no dobro da frequência da rede de alimentação. Através dessa estratégia foi possível uma redução no valor da capacitância de 86% em (COSETIN *et al.*, 2014). Na solução apresentada em (SOARES *et al.*, 2018), os parâmetros do controlador PI são calculados de forma otimizada, minimizando a capacitância de forma a manter a distorção da corrente de entrada em conformidade com a norma IEC 61000-3-2.

Em (LUZ *et al.*, 2018), é utilizado o controlador proporcional integral ressonante (PIR), dado em (2.2), onde ele possui um ganho infinito na frequência de ressonância, possuindo assim a capacidade para rastrear sinais senoidais nesta frequência.

$$PIR(s) = K_p + \frac{2K_r s}{s^2 + w_{res}^2}, \quad (2.2)$$

onde  $K_p$  é o ganho proporcional,  $w_{res}$  e  $K_r$  são a frequência e ganho ressonante, respectivamente.

Com a utilização do controlador ressonante é possível controlar a ondulação da corrente na carga LED. A referência da malha de controle é formada por um valor médio

mais uma ondulação em baixa frequência igual à ondulação da corrente de saída (o dobro da frequência da rede) (LUZ *et al.*, 2018). Com esta técnica, os autores conseguiram uma redução de 80,5% do valor nominal da capacitância.

A solução através da compensação ativa da ondulação é satisfatória quanto à redução da capacitância, pois não há a necessidade de novos circuitos ou malha de controle no sistema. No entanto, são soluções limitadas pela distorção da corrente de entrada.

## 2.2 CONTROLE ROBUSTO EM *DRIVERS* DE LED

Com relação à estratégia de controle em *drivers* de LED, muitos trabalhos utilizam o controle PI, sendo o projeto realizado por meio de teorias clássicas, tais como o lugar das raízes e diagramas de *Bode* (GRACIO *et al.*, 2011). Estas abordagens são adequadas para aplicações nas quais há um único ponto de operação, entretanto, pode levar a resultados inadequados ao se projetar sistemas com uma grande variedade de pontos de operação, como no caso de *drivers* de LED com tensão de entrada e potência variável.

Para solucionar este problema, técnicas de controle robusto são aplicadas em (CHIU; SHEN; HSIEH, 2015), onde é proposto o uso de controle robusto via LMIs em um *driver* de LED com tensão de entrada universal, visando alta robustez a variações bruscas de distúrbios e corrente de referência. Neste trabalho, o arranjo de LEDs na carga não é conhecido a priori, assim, um observador linear fuzzy é introduzido na malha de realimentação da estrutura de controle e um controlador integral T-S fuzzy é utilizado para regular a corrente na carga.

Em (WANG; TANG; HUANG, 2010; DONG; ZHANG, 2016) um controle robusto é aplicado em uma carga LED visando alcançar melhores resultados fotométricos, tais como intensidade luminosa e índice de reprodução de cores, ao realizar o controle da temperatura de junção deste componente. Em (WU; LIANG; CHEN, 1999; WANG; ZHANG; QIU, 2016) esta técnica é empregada em conversores com tensão de entrada universal.

Em (PANDEY *et al.*, 2019) são aplicadas técnicas de controle robusto em conversores buck utilizados em aplicações sensíveis a variações de operação, como fontes chaveadas, sistemas fotovoltaicos e drivers de LEDs. As estratégias propostas tratam explicitamente tanto as incertezas decorrentes de variações da tensão de entrada quanto aquelas associadas às mudanças na carga, modelando-as como distúrbios e compensando-as por meio de observadores dedicados. Dessa forma, os métodos garantem regulação precisa da tensão de saída mesmo sob perturbações significativas, além de reduzirem a necessidade de sensores.

Em (RUMBO-MORALES *et al.*, 2024) investigam o uso de controle geométrico e de controle com estrutura no infinito aplicados a um *driver* de LEDs baseado em conversor

*buck*, com ênfase na rejeição de perturbações na fonte de alimentação e na compensação de falhas no atuador. O sistema é modelado no espaço de estados, incorporando explicitamente distúrbios e falhas, o que possibilita a aplicação direta dessas técnicas de controle robusto. Os resultados demonstram que ambas as estratégias são eficazes na rejeição de perturbações constantes; entretanto, o controle geométrico apresenta melhor desempenho em cenários com falhas variáveis e mudanças de trajetória, evitando sobretensões no capacitor e oscilações excessivas de corrente. O estudo evidencia, assim, o potencial de técnicas clássicas de controle robusto, ainda pouco exploradas em eletrônica de potência, como alternativas aos métodos convencionais empregados em *drivers* de LEDs.

Já em (AHMED; IBRAHIM; OMAR, 2022), os autores propõem uma estratégia de controle robusto baseada em um condicionador unificado de qualidade de energia sem transformador (TL-UPQC) aplicado a redes extensas de iluminação por LEDs, com o objetivo de mitigar cintilação luminosa, variações de tensão e distorções harmônicas de corrente. A topologia integra um restaurador dinâmico de tensão (DVR), atuando como compensador série, e um filtro ativo de potência (APF), operando como compensador shunt, assegurando tensão senoidal no lado da carga e redução significativa do THD da corrente da rede. Os ganhos dos controladores PI são ajustados por meio do algoritmo meta-heurístico Enhanced Bald Eagle Search (EBES), apresentando desempenho superior quando comparado a outros métodos de otimização. Resultados de simulação em MATLAB demonstram a eficácia da abordagem na melhoria da qualidade de energia e na obtenção de uma rede de iluminação livre de *flicker*.

### 2.3 CONCLUSÕES PARCIAIS

Este capítulo apresenta uma revisão da literatura com foco nas técnicas destinadas à redução da capacidade empregada para filtrar a ondulação de baixa frequência na corrente da carga LED. Três abordagens foram apresentadas: estrutura de potência modificada, injeção de harmônicos e controle ativo.

A utilização de uma estrutura de potência modificada para diminuir o valor do filtro capacitivo, embora eficaz na redução dos capacitores, apresenta um aumento no número de interruptores controlados, sistemas de acionamento e complexidade nos *drivers*.

A solução de injeção de harmônicos na corrente de entrada reduz a diferença instantânea entre a potência de entrada e saída, possibilitando o uso de filtros capacitivos com valores menores. Contudo, a necessidade de duas malhas de controle torna-se complexa em sistemas de um único estágio.

A redução do filtro capacitivo por meio da ação de controle demonstra ser uma solução satisfatória. Sem a necessidade de adicionar novos circuitos e malhas de controle, é possível alcançar a redução da capacidade no sistema, mantendo a ondulação da corrente

nos LEDs. Entretanto, em conversores de estágio único, essa solução é limitada pela distorção da corrente de entrada.

No que diz respeito às técnicas de controle moderno aplicadas a *drivers* de LEDs, foram revisados os principais trabalhos que utilizam controle robusto para essa aplicação na literatura. No entanto, não foram encontradas análises na literatura que explorem a otimização  $\mathcal{H}_\infty$  visando a redução do LFR em *drivers* de LEDs, com o objetivo de diminuir o valor da capacitância empregada na filtragem dessa ondulação.

Nenhum dos trabalhos anteriores empregou essas técnicas em modelos de degradação do capacitor, onde, além de considerar a redução da capacitância, deve-se levar em conta o aumento da ESR ao longo do tempo.

### 3 TEORIA DE CONTROLE ROBUSTO

A construção de um *driver* de LED que opere na faixa de tensão universal faz com que o sistema possua pontos de operação distintos, e seu modelo dinâmico é alterado em função dessas grandezas. Com essa gama de variações paramétricas, o projeto do sistema de controle torna-se complexo, pois é necessário encontrar uma estrutura de controle capaz de garantir não apenas a estabilidade, mas também uma resposta transitória satisfatória em todos os pontos de operação.

Além das variações quanto ao modelo mencionadas anteriormente, o controlador deve garantir de forma robusta um certo nível de rejeição a distúrbios, que, neste problema, está relacionado com a capacidade de atenuar a ondulação com frequência igual ao dobro da frequência da rede de alimentação, indesejável, que aparece na forma de onda da corrente na carga. Para esta tarefa, será utilizada a otimização  $\mathcal{H}_\infty$ .

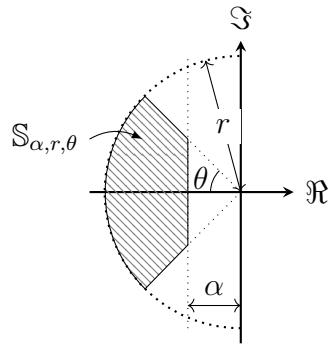

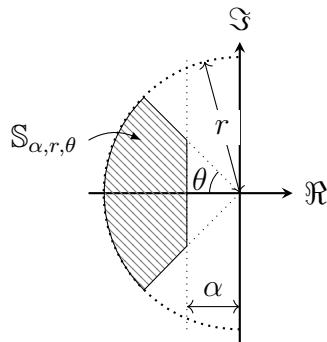

Diante dessas características, o controle robusto é uma alternativa capaz de lidar com todas essas variações no sistema, além da rejeição a distúrbios. A técnica de controle empregada será por realimentação completa de estados, em que, por meio da obtenção de um vetor de ganhos  $\mathbf{K}$ , obtido através de LMIs, será possível alocar os polos em malha fechada do sistema em uma região pré-especificada no plano complexo para qualquer ponto de operação, levando-se em conta índices de desempenho desejáveis na resposta transitória e rejeição a distúrbios.

A fim de contextualizar a aplicação prática da teoria apresentada, este capítulo também introduz um estudo de caso baseado no conversor integrado buck-boost flyback, escolhido como circuito de acionamento da carga LED. Inicialmente, foi realizada a modelagem estática, cujo objetivo consistiu no levantamento dos parâmetros de interesse do conversor e no dimensionamento de seus componentes fundamentais, considerando o princípio de funcionamento, as formas de onda características e o balanço energético entre os estágios. Em seguida, desenvolveu-se a modelagem dinâmica em pequenos sinais, indispensável para a aplicação das técnicas de controle robusto. Essa modelagem foi formulada no espaço de estados, de modo a capturar as variações paramétricas do sistema e permitir a inclusão explícita das incertezas na formulação por desigualdades matriciais lineares. Assim, o estudo de caso serve como base para a aplicação dos conceitos de estabilidade, robustez e alocação de polos que serão discutidos ao longo deste capítulo.

#### 3.1 CONTROLE POR REALIMENTAÇÃO DE ESTADOS

Para alguns conceitos que serão discutidos a seguir sobre controle robusto via LMIs, se faz necessário modelar o sistema em espaço de estados, onde será tomada como base a equação diferencial dada em (3.46).

Um sistema linear genérico com estados  $\mathbf{x} \in \mathbb{R}^n$ , entrada  $u \in \mathbb{R}$ , saída  $y \in \mathbb{R}$  e distúrbio  $w \in \mathbb{R}$  é definido pelo sistema de equações em espaço de estados

$$\begin{cases} \dot{\mathbf{x}} = \mathbf{A}\mathbf{x} + \mathbf{B}_u u + \mathbf{B}_w w \\ y = \mathbf{C}\mathbf{x} \end{cases}$$

onde  $\mathbf{A} \in \mathbb{R}^{n \times n}$ ,  $\mathbf{B}_u \in \mathbb{R}^{n \times 1}$ ,  $\mathbf{B}_w \in \mathbb{R}^{n \times 1}$  e  $\mathbf{C} \in \mathbb{R}^{1 \times n}$ .

O controle de cargas LED deve possuir as seguintes características: erro de estado estacionário nulo ao seguir uma referência constante, uma rápida resposta dinâmica sem prejudicar a operação do estágio PFC, distorcendo a corrente de entrada do sistema (ALMEIDA, 2014). Diante disso, a inclusão de um integrador é necessária para garantir um erro nulo em estado estacionário para referências constantes (OGATA, 2011).

A ação do controle integral (3.1) tem como entrada o erro do sistema  $e$ , sendo este a diferença entre a referência desejada  $ref$  e a saída  $y$ . Em (3.2), é relacionado o erro com a variável de saída.

$$\rho = \int e dt, \quad (3.1)$$

$$e = \dot{\rho} = ref - y = ref - Cx. \quad (3.2)$$

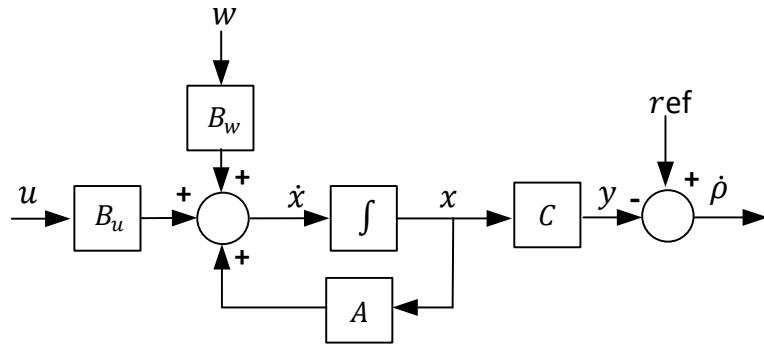

O sistema em malha aberta, com a inserção da estrutura de controle integral é ilustrado na Figura 13 e modelado por (3.3).

Figura 13 – Sistema em malha aberta.

Fonte: Elaborado pelo autor (2025).

O sistema aumentado pode ser escrito como:

$$\begin{aligned} \dot{\mathbf{x}}_a &= \mathbf{A}_a \mathbf{x}_a + \mathbf{B}_{ua} u + \mathbf{B}_{wa} w + \mathbf{B}_r ref \\ y &= \mathbf{C}_a \mathbf{x}_a \end{aligned} \quad (3.3)$$

Onde as matrizes e vetores do sistema aumentado são as seguintes:

$$\mathbf{x}_a = \begin{bmatrix} x \\ \rho \end{bmatrix}, \quad \mathbf{A}_a = \begin{bmatrix} A & 0 \\ -C & 0 \end{bmatrix}, \quad (3.4)$$

$$\mathbf{B}_{ua} = \begin{bmatrix} B_u \\ 0 \end{bmatrix}, \quad \mathbf{B}_{wa} = \begin{bmatrix} B_w \\ 0 \end{bmatrix}, \quad (3.5)$$

$$\mathbf{B}_r = \begin{bmatrix} 0 \\ 1 \end{bmatrix}, \quad \mathbf{C}_a = \begin{bmatrix} 1 & 0 \end{bmatrix}. \quad (3.6)$$

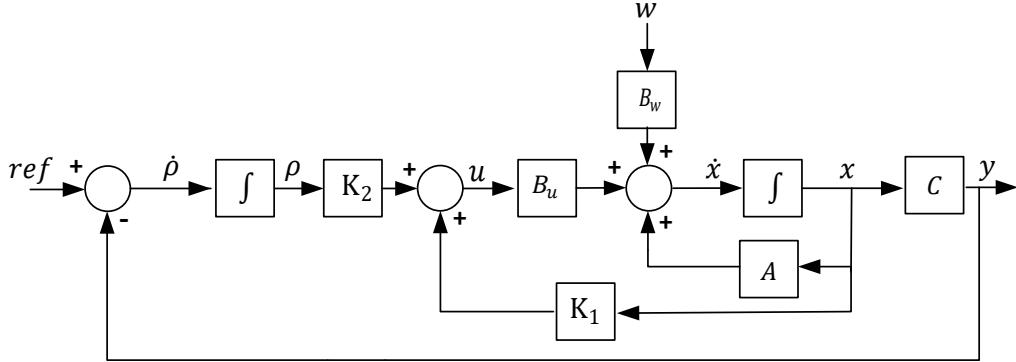

Se o sistema (3.3) é controlável pode-se alocar arbitrariamente os polos em malha fechada utilizando a seguinte ação de controle baseada na realimentação completa de estados

$$u(t) = \mathbf{K}\mathbf{x}_a(t), \quad (3.7)$$

sendo o ganho de realimentação  $\mathbf{K}$  composto da seguinte maneira:

$$\mathbf{K} = \begin{bmatrix} K_1 & K_2 \end{bmatrix}, \quad (3.8)$$

nos quais  $K_1$  e  $K_2 \in \mathbb{R}$  são os ganhos relacionados aos estados da planta e à integral do erro, respectivamente. A Figura 14, a seguir, apresenta o sistema em malha fechada com os ganhos de realimentação.

Substituindo-se a ação de controle (3.7) no modelo do sistema em malha aberta, dado por (3.3), obtém-se a seguinte equação de malha fechada para o sistema: